#### The Challenges of GNU Tool Chain Support for CORE-V

Craig Blackmore Jeremy Bennett

Copyright © 2020 Embecosm. Freely available under a Creative Commons Attribution-ShareAlike license.

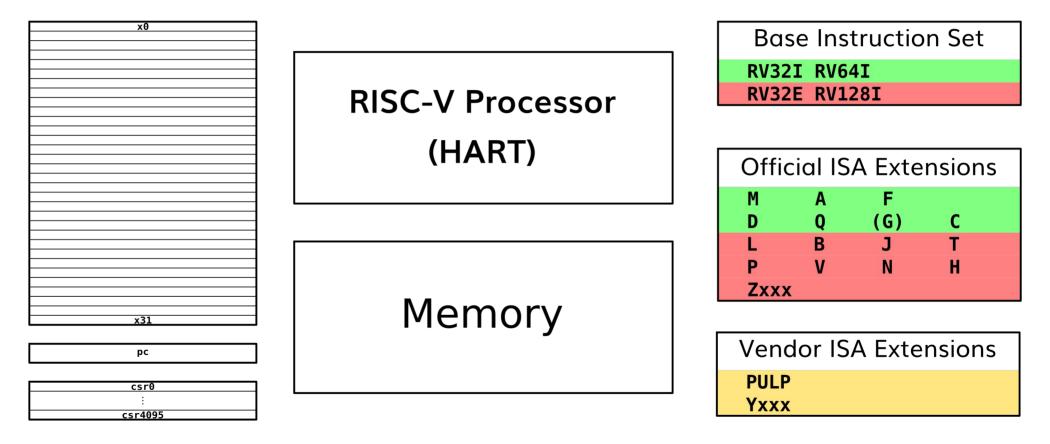

#### **RISC-V**

#### **RISC-V Instructions "Green Card"**

|                       |      | 5C-\          |                          |                          |                       |         |               |                               |             |                         |          |                      |                        |         | C-V Ref             |      |          |                      |

|-----------------------|------|---------------|--------------------------|--------------------------|-----------------------|---------|---------------|-------------------------------|-------------|-------------------------|----------|----------------------|------------------------|---------|---------------------|------|----------|----------------------|

| Base Integer          | Inst | ructions (3   | 2 64 128)                | RV Privi                 | leged Inst            |         |               |                               |             | 3 Optional FP           |          |                      |                        | Opt     | tional Compre       | ssec | d Instru | ctions: RVC          |

| Category Name         | Fm   | RV {32 0      | 54 128)I Base            | Category                 | Name                  | Fmt R   | RV mnemo      | onic                          | Cat         | tegory Name             | e Fm     | $nt = RV\{F D Q\} ($ | 'HP/SP,DP,QP)          | Catego  | <b>ry</b> Name      | Fmt  |          | RVC                  |

| Loads Load Byte       | I    | LB            | rd,rs1,imm               | CSR Access               | Atomic R/W            | R C     | CSRRW         | rd,csr,r                      | s1 Loa      | ad Loa                  | I be     | FL{W,D,Q}            | rd,rsl,imm             | Loads   | Load Word           | CL   | C.LW     | rd',rsl',imm         |

| Load Halfword         | I I  | LH            | rd,rs1,imm               | Atomic R                 | lead & Set Bit        | RC      | CSRRS         | rd,csr,r                      | s1 Sto      | ore Stor                | re S     | FS{W,D,Q}            | rs1,rs2,imm            |         | Load Word SP        |      |          | rd,imm               |

| Load Word             | 1 I  | $L\{W D Q\}$  | rd,rs1,imm               | Atomic Rea               | ad & Clear Bit        | RC      | CSRRC         | rd,csr,r                      | s1 Ari      | ithmetic AD             | D R      | FADD. {S D Q}        | rd,rs1,rs2             |         | Load Double         | CL   | C.LD     | rd',rs1',imm         |

| Load Byte Unsigned    | I I  | LBU           | rd,rs1,imm               | Ator                     | mic R/W Imm           | RC      | CSRRWI        | rd,csr,i:                     | nm          | SUBtrac                 | t R      | FSUB. {S D Q}        | rd,rs1,rs2             |         | Load Double SP      | CI   | C.LWSP   | rd,imm               |

| Load Half Unsigned    | i I  | L{H W D}U     | rd,rs1,imm               | Atomic Read 8            | k Set Bit Imm         | RC      | CSRRSI        | rd,csr,i:                     | nm          | MULtiply                | y R      | FMUL.{S D Q}         | rd,rs1,rs2             |         | Load Quad           | CL   | C.LQ     | rd',rs1',imm         |

| Stores Store Byte     | S    | SB            | rs1,rs2,imm              | Atomic Read & O          | Clear Bit Imm         | R C     | CSRRCI        | rd,csr,i                      | nm          | DIVide                  | e R      | FDIV.{S D Q}         | rd,rs1,rs2             |         | Load Quad SF        | CI   | C.LQSP   | rd,imm               |

| Store Halfword        | i S  | SH            | rs1,rs2,imm              | Change Level             | Env. Call             | RE      | ECALL         |                               |             | SQuare Roo              | T R      | FSQRT. {S D Q}       | rd,rs1                 | _ L     | oad Byte Unsigned   | CL   | C.LBU    | rd',rs1',imm         |

| Store Word            | i S  | S{W D Q}      | rs1,rs2,imm              | Environme                | nt Breakpoint         | RE      | EBREAK        |                               | Mu          | II-Add Multiply-AD      | R        | FMADD.{S D Q}        | rd,rs1,rs2,rs3         |         | Float Load Word     | CL   | C.FLW    | rd',rs1',imm         |

| Shifts Shift Left     | : R  | SLL{ W D}     | rd,rs1,rs2               | Enviror                  | nment Return          | RE      | ERET          |                               |             | Multiply-SUBtrac        | t R      | FMSUB.{S D Q}        | rd,rs1,rs2,rs3         |         | Float Load Double   | CL   | C.FLD    | rd',rs1',imm         |

| Shift Left Immediate  | e I  | SLLI {  W  D} | rd,rs1,shamt             | Trap Redirect            | t to Superviso        | R M     | ARTS          |                               | Neg         | gative Multiply-SUBtrac | t R      | FMNSUB. {S D Q}      | rd,rs1,rs2,rs3         | F       | loat Load Word SP   | CI   | C.FLWSP  | rd, imm              |

| Shift Righ            | t R  | SRL{ W D}     | rd,rs1,rs2               | Redirect Trap            | to Hypervisor         | RM      | 4RTH          |                               |             | Negative Multiply-ADD   | R        | FMNADD.{S D Q}       | rd,rs1,rs2,rs3         | Flo     | at Load Double SF   | CI   | C.FLDSP  | rd,imm               |

| Shift Right Immediate | I    | SRLI {  W  D} | rd,rs1,shamt             | Hypervisor Trap          | to Supervisor         | RH      | HRTS          |                               | Sig         | In Inject SiGN source   | e R      | FSGNJ.{S D Q}        | rd,rs1,rs2             | Stores  | Store Word          | CS   | C.SW     | rs1',rs2',im         |

| Shift Right Arithmeti | R    | SRA{ W D}     | rd, rs1, rs2             | Interrupt Wai            | it for Interrup       | RW      | 1FI           |                               |             | Negative SiGN source    |          |                      |                        |         | Store Word SF       | CSS  | C.SWSP   | rs2,imm              |

| Shift Right Arith Imn | I    |               | rd, rs1, shamt           | MMU Supe                 | ervisor FENCE         | R s     |               | rs1                           |             | Xor SiGN source         | e R      | FSGNJX. {S D Q       | } rd,rs1,rs2           |         | Store Double        | CS   | C.SD     | rs1',rs2',imr        |

| Arithmetic ADD        | R    | ADD( W D)     | rd, rs1, rs2             | Optional                 | Multiply-D            | ivide   | Extensio      | on: RV32M                     | Mii         |                         |          | FMIN. (S D Q)        | rd,rs1,rs2             | 1       | Store Double SF     | CSS  | C.SDSP   | rs2,imm              |

| ADD Immediate         |      | 1             | rd, rs1, imm             |                          | Name Fmt              |         | RV32M (I      |                               |             | MAXimum                 |          | FMAX. (SIDIO)        | rd,rs1,rs2             |         | Store Quad          |      |          | rs1',rs2',imm        |

| SUBtrac               |      |               | rd,rs1,rs2               |                          | 1ULtiply R            | MULII   | WID} re       | i,rs1,rs2                     | Co          | mpare Compare Float     |          |                      | rd,rs1,rs2             | 1       | Store Quad SF       |      |          | rs2,imm              |

| Load Upper Imn        |      | LUI           | rd, imm                  | MULtiply upp             |                       | MULH    |               | i,rs1,rs2                     |             | Compare Float <         |          | FLT. {S D Q}         | rd, rs1, rs2           |         | Float Store Word    |      |          | rd',rs1',imm         |

| Add Upper Imm to PC   |      | AUIPC         | rd, imm                  | MULtiply Half Si         |                       | MULHSU  |               | i.rsl.rs2                     |             | Compare Float ≤         |          |                      | rd,rsl,rs2             |         | Float Store Double  |      |          | rd',rsl',imm         |

| Logical XOR           | R    | XOR           | rd, rs1, rs2             | MULtiply upper H         |                       | MULHU   |               | i,rs1,rs2                     | Cat         | tegorize Classify Ty    |          |                      |                        |         | oat Store Word SF   |      |          |                      |

| XOR Immediate         |      | XORI          | rd,rs1,imm               | Divide                   | DIVide R              | DIV()   |               | i.rs1.rs2                     |             | ve Move from Intege     |          |                      | rd,rs1                 |         | at Store Double SF  |      |          |                      |

| OR                    |      | OR            | rd,rs1,rs2               | DIVide U                 |                       | DIVU    |               | i,rs1,rs2                     |             | Move to Intege          |          | FMV.X.S              | rd,rs1                 | Arithm  |                     |      | C.ADD    | rd, rs1              |

| OR Immediate          |      | ORI           | rd,rs1,rs2<br>rd,rs1,imm | RemainderRE              |                       | REM (1) |               | 1, rs1, rs2                   |             | nvert Convert from Ir   |          |                      |                        | Arithin | ADD Word            |      | C.ADD    | rd, rsi<br>rd', rs2' |

| AND AND               |      | AND           | rd,rs1,rs2               | REMainder Ur             |                       | REMU (  |               | 1, rs1, rs2<br>1, rs1, rs2    |             | nvert from Int Unsigned |          |                      |                        |         | ADD Immediate       |      | C.ADDW   | rd, imm              |

| AND Immediate         |      | ANDI          |                          |                          |                       |         |               | nsion: RVA                    | -100        |                         |          | FCVT.W. (SIDIQ)      |                        |         | ADD Word Imm        |      | C. ADDI  | rd, imm              |

|                       |      |               | rd,rs1,imm               | Category                 | Name Fmt              |         |               | 8}A (Atomic)                  | -           |                         |          | FCVT.WU.{S D Q       |                        |         |                     |      |          |                      |

| Compare Set <         |      | SLT           | rd,rs1,rs2               |                          |                       |         |               |                               |             | Convert to Int Unsigned | -        |                      |                        | -       | ADD SP Imm * 16     |      |          | 6SP ×0,imm           |

| Set < Immediate       |      | SLTI          | rd,rs1,imm               | Load Load Re             |                       | LR. {W  |               | rd,rsl                        | _           | nfiguration Read Sta    |          |                      | rd                     |         | ADD SP Imm * 4      |      |          |                      |

| Set < Unsigned        |      | SLTU          | rd,rs1,rs2               | Store Store Con          |                       | SC.{W   |               | rd,rsl,rs                     |             | Read Rounding Mode      |          | FRRM                 | rd                     |         | Load Immediate      |      | C.LI     | rd, imm              |

| Set < Imm Unsigned    |      | SLTIU         | rd,rs1,imm               | Swap                     |                       |         |               | <pre>&gt;&gt; rd,rs1,rs</pre> | _           | Read Flags              |          | FRFLAGS              | rd                     |         | Load Upper Imm      |      | C.LUI    | rd, imm              |

| Branches Branch =     |      | BEQ           | rs1,rs2,imm              | Add                      | ADD R                 |         | $D.\{W D Q\}$ |                               | _           | Swap Status Reg         |          | FSCSR                | rd,rs1                 |         | MoVe                |      | C.MV     | rd, rsl              |

| Branch a              |      | BNE           | rs1,rs2,imm              | Logical                  | XOR R                 |         | R.{W D Q]     |                               |             | Swap Rounding Mode      |          | FSRM                 | rd,rs1                 |         | SUE                 |      | C.SUB    | rd',rs2'             |

| Branch <              |      | BLT           | rs1,rs2,imm              |                          | AND R                 |         | D.{W D Q]     |                               |             | Swap Flags              |          |                      | rd,rs1                 |         | SUB Word            |      |          | rd',rs2'             |

| Branch 2              |      | BGE           | rs1,rs2,imm              |                          | OR R                  |         | .{W D Q}      |                               |             | ap Rounding Mode Imm    |          | FSRMI                | rd,imm                 | Logical |                     |      | C.XOR    | rd',rs2'             |

| Branch < Unsigned     |      | BLTU          | rs1,rs2,imm              | Min/Max MI               |                       |         | N.{W D Q]     |                               |             | Swap Flags Imm          |          | FSFLAGSI             | rd,imm                 | -       | OR                  |      | C.OR     | rd',rs2'             |

| Branch ≥ Unsigned     |      | BGEU          | rs1,rs2,imm              | -11                      | Ximum R               |         | X.{W D Q]     |                               |             | 3 Optional FP Exte      |          |                      |                        | -       | AND                 |      | C.AND    | rd',rs2'             |

| Jump & Link J&L       |      | JAL           | rd,imm                   | MINimum U                |                       |         |               | <pre>&gt;&gt; rd,rs1,rs</pre> | · –         | tegory Name             |          |                      | 'HP/SP,DP,QP)          |         | AND Immediate       |      |          | rd',rs2'             |

| Jump & Link Registe   |      | JALR          | rd,rsl,imm               | MAXimum Ur               | nsigned R             | AMOMA   | XU.{W D Ç     | <pre>&gt;&gt; rd,rs1,rs</pre> | 2 <b>Mo</b> | ve Move from Intege     |          |                      | rd,rs1                 | Shifts  | Shift Left Imm      |      | C.SLLI   | rd, imm              |

| Synch Synch thread    |      | FENCE         |                          |                          |                       |         |               |                               |             | Move to Intege          |          | FMV.X.{D Q}          | rd,rs1                 |         | 't Right Immediate  |      | C.SRLI   | rd',imm              |

| Synch Instr & Data    | I    | FENCE.I       |                          | -                        |                       |         |               |                               | Co          | nvert Convert from Ir   |          |                      |                        | Sh      | ift Right Arith Imm | CB   | C.SRAI   | rd',imm              |

| System System CALL    | . I  | SCALL         |                          |                          |                       |         |               |                               | Co          | nvert from Int Unsigned |          | FCVT.{S D Q}.        |                        | Branch  |                     |      | C.BEQZ   | rsl',imm             |

| System BREAK          |      | SBREAK        |                          | 16-bit (RVC)             | and 32-bit            | Instru  | iction For    | mats                          |             | Convert to In           |          | FCVT.{L T}.{S        |                        |         | Branch≠0            | CB   | C.BNEZ   | rs1',imm             |

| Counters ReaD CYCLE   | I    | RDCYCLE       | rd                       |                          |                       |         |               |                               |             | Convert to Int Unsigned | I R      | FCVT.{L T}U.{        | S D Q} rd,rs1          | Jump    | Jump                | CJ   | C.J      | imm                  |

| ReaD CYCLE upper Hal  | fI   | RDCYCLEH      | rd                       | CI 15 14 13 15<br>funct4 | 2 11 10 9 8<br>rd/rs1 | 765     |               | 00                            |             |                         |          |                      |                        |         | Jump Register       | CR   | C.JR     | rd, rsl              |

| ReaD TIME             |      | RDTIME        | rd                       | CSS funct3 im            |                       |         |               | op R 31                       | 30          |                         | 19       |                      | 8 7 6 0                | Jump 8  |                     |      | C.JAL    | imm                  |

| ReaD TIME upper Hal   |      | RDTIMEH       | rd                       | CIW funct3               | imm                   |         | rs2           | op I -                        | funct       | 7 rs2<br>imm[11:0]      | IS<br>IS |                      | rd opcode<br>rd opcode |         | mp & Link Register  |      |          | rsl                  |

| ReaD INSTR RETire     |      | RDINSTRET     |                          | CL funct3                | imm                   |         | rď            | 0p                            | imm 11      |                         | IS<br>IS |                      | m[4:0] opcode          | System  |                     |      |          |                      |

| ReaD INSTR upper Hal  |      | RDINSTRETH    |                          | CS funct3                | imm rsl<br>imm rsl    |         |               |                               | 12 in       |                         | IS       |                      | imm[11] opcode         |         |                     |      |          |                      |

| and a second appendix |      |               |                          |                          | offset rsl            |         |               |                               |             | imm[31:12]              |          |                      | rd opcode              |         |                     |      |          |                      |

|                       |      |               |                          | CJ funct3                |                       | target  |               | op UJ imr                     | n[20]       | imm[10:1] imm[11]       | i        |                      | rd opcode              |         |                     |      |          |                      |

|                       |      |               |                          |                          |                       |         |               | .01                           |             |                         |          |                      |                        |         |                     |      |          |                      |

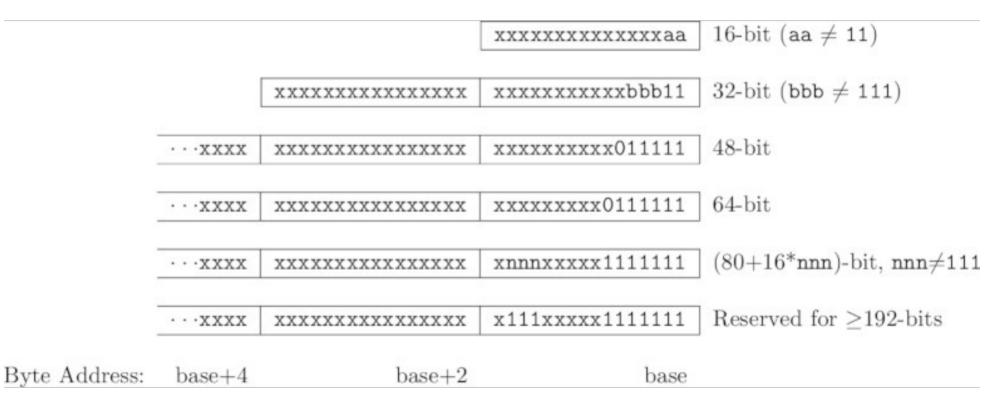

#### **RISC-V Extensible Instructions**

#### **RISC-V 32-Bit Instruction Formats**

| Format             |                     | Bit |     |       |      |            |    |            |     |     |    |    |        |        |     |    |        |        |    |    |          |      |   |      |   |        |    |      |   |   |     |

|--------------------|---------------------|-----|-----|-------|------|------------|----|------------|-----|-----|----|----|--------|--------|-----|----|--------|--------|----|----|----------|------|---|------|---|--------|----|------|---|---|-----|

| Format             | 31                  | 30  | 29  | 28    | 27   | 26         | 25 | 24         | 23  | 22  | 21 | 20 | 19     | 18     | 17  | 16 | 15     | 14     | 13 | 12 | 11       | 10   | 9 | 8    | 7 | 6      | 5  | 4    | 3 | 2 | 1 0 |

| Register/register  | funct7 rs2          |     |     |       |      | rs1 funct3 |    |            |     | rd  |    |    |        | opcode |     |    |        |        |    |    |          |      |   |      |   |        |    |      |   |   |     |

| Immediate          | imm[11:0]           |     |     |       |      |            |    | rs1 funct3 |     |     |    | 3  | rd     |        |     |    | opcode |        |    |    |          |      |   |      |   |        |    |      |   |   |     |

| Upper<br>immediate | imm[31:12] rd       |     |     |       |      |            |    |            |     |     |    |    |        | opcode |     |    |        |        |    |    |          |      |   |      |   |        |    |      |   |   |     |

| Store              |                     |     | imn | n[11: | 5]   |            |    |            |     | rs2 |    |    |        |        | rs1 |    |        | funct3 |    |    | imm[4:0] |      |   |      |   | opcode |    |      |   |   |     |

| Branch             | [12]                |     | i   | mm[   | 10:5 | ]          |    |            | rs2 |     |    |    |        | rs1    |     |    | f      | unct   | 3  | i  | mm[⁄     | 4:1] |   | [11] |   |        | op | bcod | Э |   |     |

| Jump               | [20] imm[10:1] [11] |     |     |       |      | imm[19:12] |    |            |     | rd  |    |    | opcode |        |     |    |        |        |    |    |          |      |   |      |   |        |    |      |   |   |     |

#### opcode = xxbbb11

| bbb | 000    | 001      | 010   | 011      | 100    | 101   | 110              | 111    |

|-----|--------|----------|-------|----------|--------|-------|------------------|--------|

| xx  |        |          |       |          |        |       |                  | (>32b) |

| 00  | LOAD   | LOAD-FP  |       | MISC-MEM | OP-IMM | AUIPC | <b>OP-IMM-32</b> | 48b    |

| 01  | STORE  | STORE-FP |       | AMO      | OP     | LUI   | 0P-32            | 64b    |

| 10  | MADD   | MSUB     | NMSUB | NMADD    | OP-FP  |       |                  | 48b    |

| 11  | BRANCH | JALR     |       | JAL      | SYSTEM |       |                  | ≥ 80b  |

#### opcode = xxbbb11

| bbb | 000    | 001      | 010      | 011      | 100    | 101      | 110              | 111    |

|-----|--------|----------|----------|----------|--------|----------|------------------|--------|

| xx  |        |          |          |          |        |          |                  | (>32b) |

| 00  | LOAD   | LOAD-FP  |          | MISC-MEM | OP-IMM | AUIPC    | <b>OP-IMM-32</b> | 48b    |

| 01  | STORE  | STORE-FP |          | AMO      | OP     | LUI      | 0P-32            | 64b    |

| 10  | MADD   | MSUB     | NMSUB    | NMADD    | OP-FP  | reserved |                  | 48b    |

| 11  | BRANCH | JALR     | reserved | JAL      | SYSTEM | reserved |                  | ≥ 80b  |

#### opcode = xxbbb11

| bbb | 000    | 001      | 010      | 011      | 100    | 101      | 110              | 111    |

|-----|--------|----------|----------|----------|--------|----------|------------------|--------|

| xx  |        |          |          |          |        |          |                  | (>32b) |

| 00  | LOAD   | LOAD-FP  | custom-0 | MISC-MEM | OP-IMM | AUIPC    | <b>OP-IMM-32</b> | 48b    |

| 01  | STORE  | STORE-FP | custom-1 | AMO      | 0P     | LUI      | 0P-32            | 64b    |

| 10  | MADD   | MSUB     | NMSUB    | NMADD    | OP-FP  | reserved | custom-2         | 48b    |

| 11  | BRANCH | JALR     | reserved | JAL      | SYSTEM | reserved | custom-3         | ≥ 80b  |

#### opcode = xxbbb11

| bbb | 000    | 001      | 010      | 011      | 100    | 101      | 110              | 111    |

|-----|--------|----------|----------|----------|--------|----------|------------------|--------|

| xx  |        |          |          |          |        |          |                  | (>32b) |

| 00  | LOAD   | LOAD-FP  | custom-0 | MISC-MEM | OP-IMM | AUIPC    | <b>OP-IMM-32</b> | 48b    |

| 01  | STORE  | STORE-FP | custom-1 | AMO      | 0P     | LUI      | 0P-32            | 64b    |

| 10  | MADD   | MSUB     | NMSUB    | NMADD    | OP-FP  | reserved | custom-2         | 48b    |

| 11  | BRANCH | JALR     | reserved | JAL      | SYSTEM | reserved | custom-3         | ≥ 80b  |

custom-2 and custom-3 are also reserved for RV128

## Parallel Ultra Low Power (PULP)

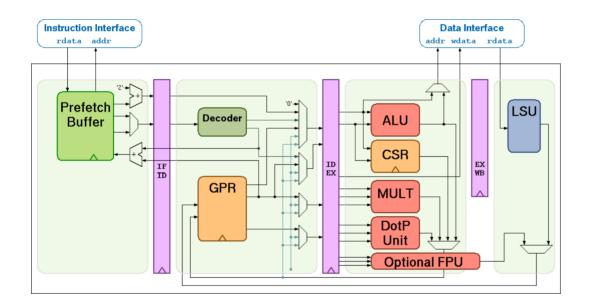

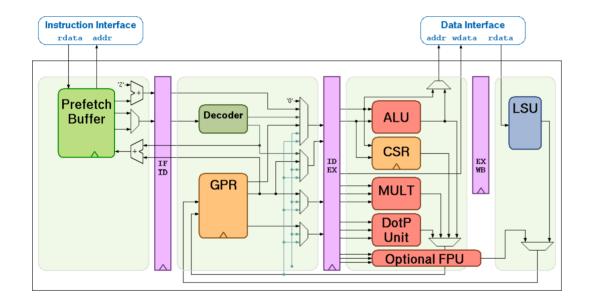

#### **PULP RI5CY core**

- 4-stage, in-order

- 32-bit RV32IMFC

- PULP custom extensions

- post-inc load/store

- multiply-accumulate

- ALU extensions

- hardware loops

- bit manipulation

- SIMD

### **RISC-V** Organizations

### **CORE-V RV32E40P**

**OpenHW Group CORE-V CV32E40P**

- 4-stage, in-order

- 32-bit RV32IMFC

- PULP custom extensions

- post-inc load/store

- multiply-accumulate

- ALU extensions

- hardware loops

- bit manipulation

- SIMD

## PULP RI5CY → CORE-V CV32E40P

- Hardware

- robust verification program

## PULP RI5CY → CORE-V CV32E40P

- Hardware

- robust verification program

- Software

- need GNU tools, Clang/LLVM tools

- need RTOS and full-fat OS

- need IDEs

- need simulators

## PULP RI5CY → CORE-V CV32E40P

- Hardware

- robust verification program

- Software

- need GNU tools, Clang/LLVM tools

- need RTOS and full-fat OS

- need IDEs

- need simulators

- Reference platform for FPGA use

## **CORE-V CV32E40P GNU Tools**

- Full GNU tool chain supporting

- ~150 new instruction types

- $\sim$ 350 if you count all the variants

- based on GCC 7.1

# CORE-V CV32E40P GNU Tools

- Full GNU tool chain supporting

- ~150 new instruction types

- $\sim$ 350 if you count all the variants

- based on GCC 7.1

- University research compiler

- no tests (not even the upstream ones)

- no adherence to GNU coding standards

- tramples all over reserved RISC-V coding space

## **CORE-V GNU Tools Strategy**

- Move instruction encoding to *custom*[0123] (hardware)

- blocker on any upstreaming

- leave out SIMD and bit manipulation

- being standardized officially

- Update GNU tool chain

- add tests to existing (2017) PULP binutils-gdb

- roll forward to 2020 binutils-gdb

- port PULP GCC changes to 2020 GCC

## **CORE-V GNU Tools Progress**

- Back-porting tests to 2017 binutils-gdb failed

- too much other research code in the way

- RISC-V binutils-gdb port has changed much in 3 years

## **CORE-V GNU Tools Progress**

- Back-porting tests to 2017 binutils-gdb failed

- too much other research code in the way

- RISC-V binutils-gdb port has changed much in 3 years

- Restart adding PULP commits to 2020 binutils-gdb

- selective choice of just CORE-V features

## **CORE-V GNU Tools Progress**

- Back-porting tests to 2017 binutils-gdb failed

- too much other research code in the way

- RISC-V binutils-gdb port has changed much in 3 years

- Restart adding PULP commits to 2020 binutils-gdb

- selective choice of just CORE-V features

- Should we use CGEN instead?

- already have a full RISC-V implementation

## Upstreaming

- Central principle for the OpenHW Group

- open source work must be contributed back and shared

- Choose a target "triplet" for non-official RISC-V

- arch-subarch-vendor-os-environment

- riscv32-corev-none-elf (for bare metal)

- Add architecture options -march=Ycorev-xxx

- allows discrimination between CORE-V features

- Start with binutils-gdb, then GCC, then newlib

#### **Poll: Is This the Right Approach?**

A) Yes

#### B) No

#### **Thank You**

craig.blackmore@embecosm.com jeremy.bennett@embecosm.com openhwgroup.org Craig Blackmore Jeremy Bennett

Copyright © 2020 Embecosm. Freely available under a Creative Commons Attribution-ShareAlike license.