# Teaching perf to show processor hazards

Madhavan Srinivasan maddy@linux.vnet.ibm.com Linux Technology Centre - IBM

#### Agenda

- Processor Pipeline

- Pipeline issues/Hazard

- IBM Processor Sampling support

- Perf API arch neutral interface

- Perf tool options and enhancements

- Screenshot

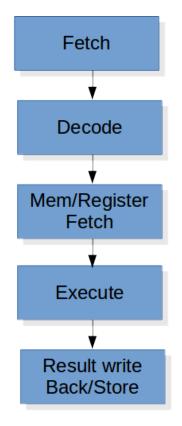

#### Instruction cycle

- Processing instruction includes these steps

- Fetch opcode

- Decode stage

- register/memory fetch based on opcode type

- Execute instruction

- write-back/store the result

Basic Instruction pipeline

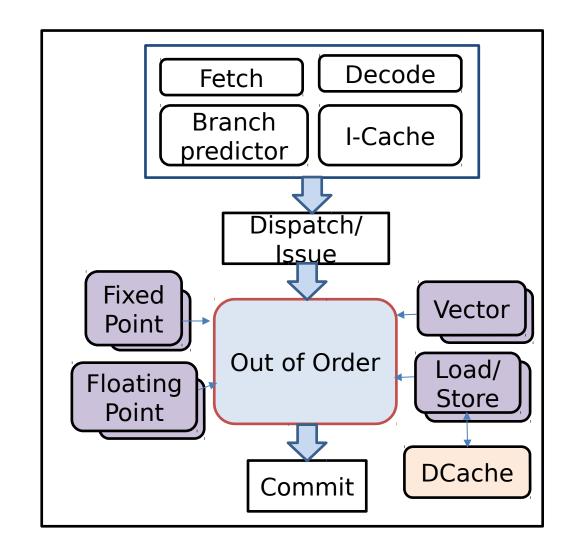

#### Instruction cycle

- Most modern microprocessors employ complex instruction execution (pipelined superscalar)

- Multiple instruction in parallel

- more execution units

- Execution unit divided in different stages

- Speculation/OOO Execution

- Multiple different pipelines/Sub-pipelines

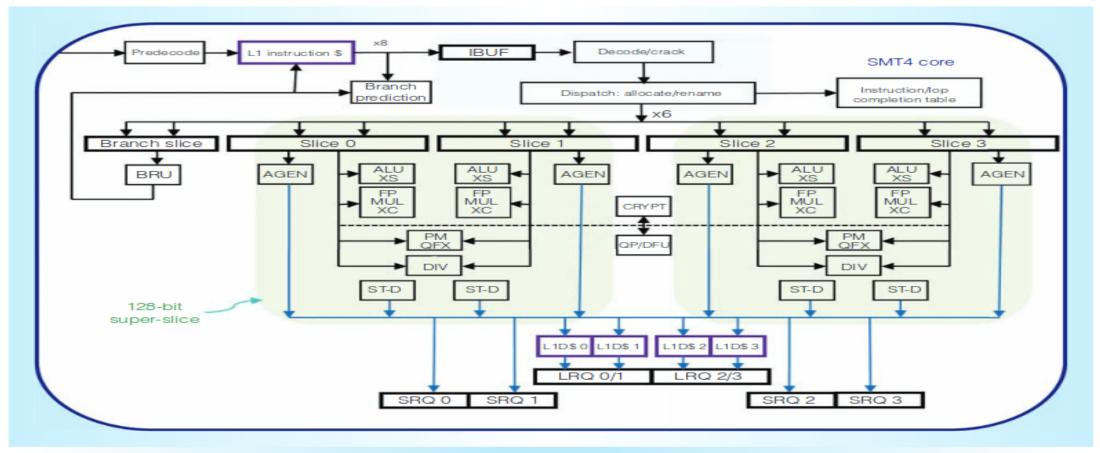

#### Example: IBM Power9

Figure 5. Power9 SMT4 core. The detailed core block diagram shows all the key components of the Power9 core.

Source: IBM Power9 Processor Architecture. Satish Kumar Sadasivam; Brian W. Thompto; Ron Kalla; William J. Starke. IEEE Micro, Volume 37, Issue 2, 2017.

5 / 20

https://ieeexplore.ieee.org/document/7924241?section=abstract

#### Performance (Instruction per Cycles)

- Increases Stall cycles

- Reduce workload performance

- Lowers Instruction per cycles

- Hazard

#### Hazards

- Prevent the next instruction in the instruction stream from being executing during its designated clock cycle

- Performance hit

- Classes of Hazards:

- Structural

- part of the processor's hardware is needed by two or more instructions at the same time

- Control

- conditional branches interfere with instruction fetches in a pipeline

- Data

- instructions that exhibit data dependence modify data in different stages of a pipeline

- Read after Write (RAW) hazards, also known as true dependences

- Write after Write (WAW) hazards, also known as output dependences

- Write after Read (WAR) hazards, also known as antidependences

#### IBM Power Processor Sampling Support

- Why sample

- Identification of hotspots in code/data and performancesensitive areas

- Mark (sample) an instruction and collection details

- 64bit register records details about marked instruction during its lifetime in pipeline

- Power ISA provides three special purpose registers

- Sampled Instruction Address Register (SIAR)

- Sampled Data Address Register (SDAR)

- Sample Instruction Event Register (SIER)

• Source: https://www-355.ibm.com/systems/power/openpower/tgcmDocumentRepository.xhtml?aliasId=POWER9\_Sforza#

#### Why perf?

- Performance tool used by eco-system

- Provides access to Performance Monitoring Unit (PMU)

- Allows to closer look at hardware behaviour

- Capability to generate reports out of data collected

- It is fast, lightweight and precise

#### Why add hazard information in perf

- perf today support exporting memory sampling information

- PERF\_SAMPLE\_DATA\_SRC and PERF\_SAMPLE\_WEIGHT

- Based on hardware support, it expose

- Instruction class (load, store ....)

- where the data came from (memory hierarchy, hit, hitm, miss)

- how long did it took for the reload (time in cycles)

- Data translation (TLB), snoop

| Samples: 7 of event 'cpu/mem-loads/pp', Event count (approx.): 66 |                                 |                   |               |        |        |              |       |                         |

|-------------------------------------------------------------------|---------------------------------|-------------------|---------------|--------|--------|--------------|-------|-------------------------|

| Overhead                                                          | Symbol                          | Shared Object     | Memory access | Weight | Locked | TLB access   | Snoop | Data Symbol             |

| 37.88%                                                            | [k] queue_work_on               | [kernel.kallsyms] | L1 hit        | 25     | Yes    | L1 or L2 hit | None  | [k] 0xffff88021f94a408  |

| 10.61%                                                            | [.]overflow@plt                 | ls                | L1 hit        | 7      | No     | L1 or L2 hit | None  | [.] 0x000000000061e150  |

| 10.61%                                                            | [k] account_entity_enqueue      | [kernel.kallsyms] | L1 hit        | 7      | No     | L1 or L2 hit | None  | [k] 0xffff88022dc97380  |

| 10.61%                                                            | [k] attach_entity_load_avg      | [kernel.kallsyms] | L1 hit        | 7      | No     | L1 or L2 hit | None  | [k] 0xffff8802207ebae0  |

| 10.61%                                                            | [k] nmi_cpu_backtrace           | [kernel.kallsyms] | L1 hit        | 7      | No     | L1 or L2 hit | None  | [k] 0xfffff88022dc48e20 |

| 10.61%                                                            | <pre>[k] unmap_page_range</pre> | [kernel.kallsyms] | L1 hit        | 7      | No     | L1 or L2 hit | None  | [k] 0xffff88018f7f3ad0  |

| 9.09%                                                             | [.] 0x00000000000ddc1           | ls                | L1 hit        | 6      | No     | L1 or L2 hit | None  | [.] 0x00007ffc2baec668  |

#### Challenges extending -- perf\_mem\_data\_src

- perf\_mem\_data\_src intended for memory sampling

- Not enough bits to expose

- pipeline stage

- hazard reason

- Stall reason

- Other instruction class

```

#if defined( LITTLE ENDIAN BITFIELD)

union perf mem data src {

u64 val;

struct {

/* type of opcode */

mem_op:5,

/* memory hierarchy level */

mem lvl:14,

/* snoop mode */

mem_snoop:5,

mem lock:2.

/* lock instr */

mem dtlb:7,

/* tlb access */

mem lvl num:4, /* memory hierarchy level number *

mem_remote:1,

/* remote */

mem snoopx:2,

/* snoop mode, ext */

mem rsvd:24:

};

#elif defined( BIG ENDIAN BITFIELD)

union perf_mem_data_src {

__u64 val;

struct {

u64

mem_rsvd:24,

/* snoop mode, ext */

mem snoopx:2,

/* remote */

mem remote:1,

mem lvl num:4.

/* memory hierarchy level number *

mem dtlb:7,

/* tlb access */

mem lock:2,

/* lock instr */

mem snoop:5,

/* snoop mode */

/* memory hierarchy level */

mem_lvl:14,

/* type of opcode */

mem op:5;

};

#error "Unknown endianness'

```

#### Approach to export hazard data via *perf*

- Struct to collect hazard data

- Sampling type/format

- Tool option to notify hazard data collection

- New reporting mode to present the hazard data

- Optional new built-in tool (wrapper for perf record)

- Capture and present Hazard data Usability

- Similar to "perf mem"

#### Hazard data – perf screenshot

```

# Samples: 41 of event 'r401e0'

# Event count (approx.): 28124

# Sort order : sym,dso,class,hazard_stage,hazard_reason,stall_stage,stall_reason,icache,type

Shared Object

Stall Stage Stall Reason

# Overhead Symbol

Instruction Class Hazard Stage Hazard Reason

ICache acc

[.] 0x00000000000b0414

L2 hit

libc-2.26.so

Load

TLB Miss

[k] get_mem_cgroup_from_mm

[kernel.kallsyms]

Resource Collision

Dcache miss

L2 hit

Load

IIU

[.] 0x00000000000b0400

Floating Point

libc-2.26.so

Resource Collision

L2 hit

[.] 0x00000000000b03fc

libc-2.26.so

LSU

TLB Miss

L2 hit

Load

[.] 0x00000000000b0400

libc-2.26.so

L2 hit

Store

[.] 0x00000000000b040c

libc-2.26.so

Floating Point

Resource Collision

L2 hit

Others

[.] 0x000000000000b0408

libc-2.26.so

L2 hit

Store

[.] 0x00000000000b041c

Fixed point

L2 hit

libc-2.26.so

```

#### perf\_pipeline\_haz\_data

- Pipeline Stages as u32

- Arch can decide how many

- Bit mask or Value as index

- Hazard and stall reasons as separate fields

- Cleaner implementation

- Multiple hazard representation

- Instruction cache hierarchy

- Processor version

- tool side to post process

```

struct perf pipeline haz data {

/* Class: Load, Store, Branch */

class:

/* Type: Multiple/Single cycle/byte */

type;

/* Instruction Cache source

icache:

u32

/* Suffered hazard in pipeline stage */

hazard stage;

/* Hazard reason */

hazard reason;

/* Suffered Stall in pipeline stage */

stall_stage;

u32

/* Stall reason */

stall_reason;

/* Processor Version information */

u32

proc ver;

```

# perf\_pipeline\_haz\_data - struct to collect hazard data

- Added new perf sample type/format

- PERF\_SAMPLE\_PIPELINE\_HAZ

- Proposed to be part of include/uapi/linux/perf\_event.h

- Macros could be part of arch folder

(ex.. arch/powerpc/include/uapi/as m/perf\_pipeline\_haz.h

```

Macros for the Instruction Class */

enum perf_pipleline_inst_class {

PERF PIPELINE ICLASS LOAD = 1.

PERF PIPELINE ICLASS STORE,

PERF PIPELINE ICLASS BRANCH,

PERF_PIPELINE_ICLASS_FP,

PERF PIPELINE ICLASS FX,

PERF_PIPELINE_ICLASS_IFU_NON_BRANCH,

* Macros for Pipeline units */

enum perf_pipeline_stage {

PERF_PIPELINE_STAGE_IFU = 1,

PERF PIPELINE STAGE_IDU,

PERF_PIPELINE_STAGE_IIU,

PERF_PIPELINE_STAGE_LSU,

PERF PIPELINE STAGE BR,

PERF PIPELINE STAGE FX,

PERF PIPELINE STAGE FP,

PERF PIPELINE STAGE VX,

^{\prime *} Macros for the Instruction Cache ^{*}/

#define HAZ ICACHE SHIFT

(x) << (HAZ_ICACHE_SHIFT)</pre>

#define HAZ_ICACHE_VAL(x)

#define HAZ ICACHE HIT

#define HAZ ICACHE MISS

0x2

enum perf_pipeline_icache {

PERF PIPELINE ICACHE L1 = 1,

PERF PIPELINE ICACHE L2,

PERF_PIPELINE_ICACHE_L3,

```

#### perf tool -- Enhancements for hazard capture

- New perf tool option

- User to indicate hazard data capture

- Proposing "-H" as option

- Needed to enable attr\_sample\_type

```

#./perf record -H -e r401e0 ./ebizzy -t 1 -S 1 -m 4096

24166 records/s

real 1.00 s

user 0.43 s

sys 0.57 s

[ perf record: Woken up 1 times to write data ]

[ perf record: Captured and wrote 0.005 MB perf.data (45 samples) ]

#

```

Raw event "r401e0" used here is "PM\_MRK\_INST\_CMPL" which enables IBM Power processor sampling support to capture hazard/stall data

#### perf tool – Enhancements for hazard capture

- Support functions to present raw hazard structure data

- Perf report "-D" support

Screenshot show one PERF\_RECORD\_SAMPLE data output from "perf report - D" command. Presents all the elements of *perf\_pipeline\_haz\_data* struct

#### hazard-info – perf report enhancement

- New "--hazard-info" mode

- Support new –sort types

- Focused on hazard data presentation

```

# Samples: 41 of event 'r401e0'

# Event count (approx.): 28124

# Sort order : sym,dso,class,hazard_stage,hazard_reason,stall_stage,stall_reason,icache,type

# Overhead Symbol

Shared Object

Instruction Class Hazard Stage Hazard Reason

Stall Stage Stall Reason

ICache acc

[.] 0x00000000000b0414

libc-2.26.so

TLB Miss

L2 hit

Load

Resource Collision

[k] get_mem_cgroup_from_mm

[kernel.kallsyms]

Dcache miss

L2 hit

LSU

libc-2.26.so

0x00000000000b0400

L2 hit

Floating Point

Resource Collision

L2 hit

0x000000000000b03fc

libc-2.26.so

TLB Miss

Load

0x00000000000b0400

libc-2.26.so

Store

L2 hit

libc-2.26.so

Resource Collision

L2 hit

0x00000000000b040c

Floating Point

Others

0x000000000000b0408

libc-2.26.so

Store

L2 hit

L2 hit

[.] 0x00000000000b041c

libc-2.26.so

Fixed point

```

### Legal Statement

- This work represents the view of the authors and does not necessarily represent the view of the employers (IBM Corporation).

- IBM and IBM (Logo) are trademarks or registered trademarks of International Business Machines in United States and/or other countries.

- Linux is a registered trademark of Linus Torvalds.

- Other company, product and service names may be trademarks or service marks of others.

## Thank you