TOKYO, JAPAN / DECEMBER 11-13, 2025

# Preparing RISC-V Linux for RVA23

### Why should the kernel add support for RVA23?

- Standardization around a set of configs for performant hardware

- Enable broad-sweeping optimizations for RVA23 hardware

- Improve developer experience around extension support and discovery

RFC available here: <a href="https://lore.kernel.org/linux-riscv/20251210-profiles-v1-0-315a6ff2ca5a@gmail.com/T/#t">https://lore.kernel.org/linux-riscv/20251210-profiles-v1-0-315a6ff2ca5a@gmail.com/T/#t</a>

### Standardization around a set of configs for performant hardware

- Introduce a new defconfig "rva23\_defconfig" that is focused on server platforms

- This will be based on a new rva23 config, and be portable to all rva23 compatible platforms

- "defconfig" will continue to be used to build a kernel that can run on any platform

#### RVA23

#### Profiles: An attempt to wrangle the inherent fragmentation of the riscv ISA

- RVA23 targets server-class and application processors

- Notably requires:

- Vector

- Hypervisor

- May-be-ops

- Performance counter overflows.

## Example is a string for rva23 compatible hardware

rv64mafdcbvh\_zicsr\_zicntr\_zihp m\_ziccif\_ziccrse\_ziccrse\_ziccamo a\_zicclsm\_za64rs\_zihintpause\_zi c64b\_zicbom\_zicbop\_zicboz\_zfh min\_zkt\_zihintntl\_zicond\_zimop\_zcmop\_zcb\_zfa\_zawrs\_supm\_sva de\_ssccptr\_sstvecd\_sstvala\_ssco unterenw\_svpbmt\_svinval\_svnap ot\_sstc\_sscofpmf\_ssnpm\_ssu64x l\_sstateen\_shcounterenw\_shvstv ala\_shtvala\_shvstvecd\_shvsatpa\_shgatpa

### Enable broad-sweeping optimizations for RVA23 hardware

- Split extensions into "enabled", "supported", and "disabled"

- RVA23 config will select "enabled" for all mandatory extensions

- These extensions can then be added to the compiler's march

- Focus performance optimizations on a kernel where extensions are compiled into it rather than discovered at runtime

#### riscv\_has\_extension\_\* optimization

```

if (riscv_has_extension_likely(EXT)) {

alternative

} else {

fallback

Enabled

Supported

Disabled

nop

alternative

j end

Discovered in isa string

fallback

alternative

no

fallback

end:

jno

alternative

j end

Not discovered in isa string

fallback

alternative

no:

fallback

end:

```

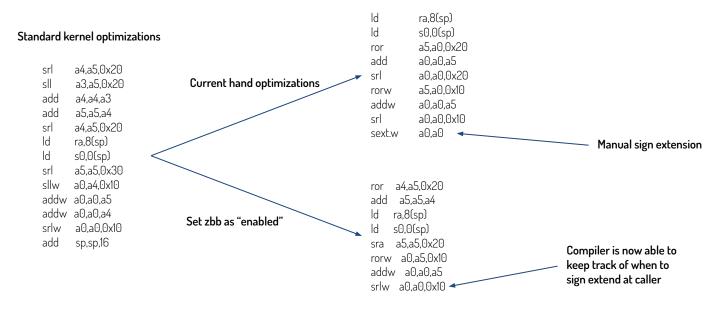

## Eliminate hand-coded assembly routines Example: do\_csum\_no\_alignment()

(Also: The riscv compiler has gotten a lot better over the years and can properly optimize more sequences now)

### Improve developer experience around extension support and discovery

Globally enabled extensions simplify writing optimized code

- When code is guarded by CONFIG\_RISCV\_ISA\_EXT and CONFIG\_TOOLCHAIN\_HAS\_EXT, the extension is available to the compiler so ".option arch" can be dropped

What happens when trying to boot the rva23 kernel on non-compliant hardware?

It will crash.

# What happens when trying to boot the rva23 kernel on non-compliant hardware and it doesn't crash?

- The hardware supports enough instructions that any that are not supported are not being emitted by the kernel or the compiler

- The isa string could be checked and a warning thrown with which extensions are expected but not found

### Should we add support for "rva23" in the isa string?

- The isa string is *really* long

- The developer only needs to add on additional extensions their platform supports

- Requires changes everywhere (QEMU, OpenSBI, applications reading /proc/cpu, etc...)

TOKYO, JAPAN / DECEMBER 11-13, 2025