Richmond, Virginia | November 13-15, 2023

# Linux Perf Tool Metrics

Ian Rogers (Google) Weilin Wang (Intel)

# Getting started

Linux

Perf Tool

#### Metrics

Let's ask perf!

# Getting started

Linux

Perf Tool

#### Metrics

#### Getting started

Linux

Perf Tool

Metrics

# Getting started

Linux

Perf Tool

Metrics

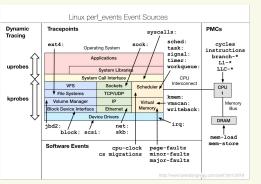

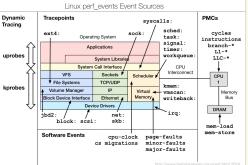

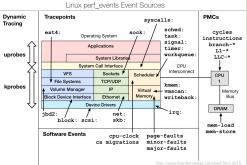

## Why metrics?

Events are good but have interesting properties:

- What are the units of a counter? Bytes, cache lines, cycles, instructions, different clocks. Are speculative instructions counted?

- Perf will aggregate the same event across multiple PMUs (e.g. memory controllers) and events can be scaled.

Metrics allow for multiple different counters to be combined across different PMUs, incorporating things like time and outputting with human readable units.

**Event**

#### How events are encoded

\$ ls /sys/bus/event\_source/devices/cpu/events

branch-instructions cpu-cycles slots

branch-misses instructions topdown-bad-spec

bus-cycles mem-loads topdown-be-bound

cache-misses mem-stores topdown-fe-bound

cache-references ref-cycles topdown-retiring

#### linux / tools / perf / pmu-events / arch / x86 / meteorlake / memory.json

| Code | Blame | 356 lines (356 loc) · 16.3 KB 🔀 Code 55% faster with GitHub Copilot                                |

|------|-------|----------------------------------------------------------------------------------------------------|

| 131  | },    |                                                                                                    |

| 132  | {     |                                                                                                    |

| 133  |       | "BriefDescription": "Counts the number of memory ordering machine clears due to memory renaming.", |

| 134  |       | "EventCode": "0x09",                                                                               |

| 135  |       | "EventName": "MEMORY_ORDERING.MRN_NUKE",                                                           |

| 136  |       | "SampleAfterValue": "100003",                                                                      |

| 137  |       | "UMask": "0x2",                                                                                    |

| 138  |       | "Unit": "cpu_core"                                                                                 |

| 139  | },    | •                                                                                                  |

| 140  | {     |                                                                                                    |

```

$ perf list --details

```

Seeing metric expressions

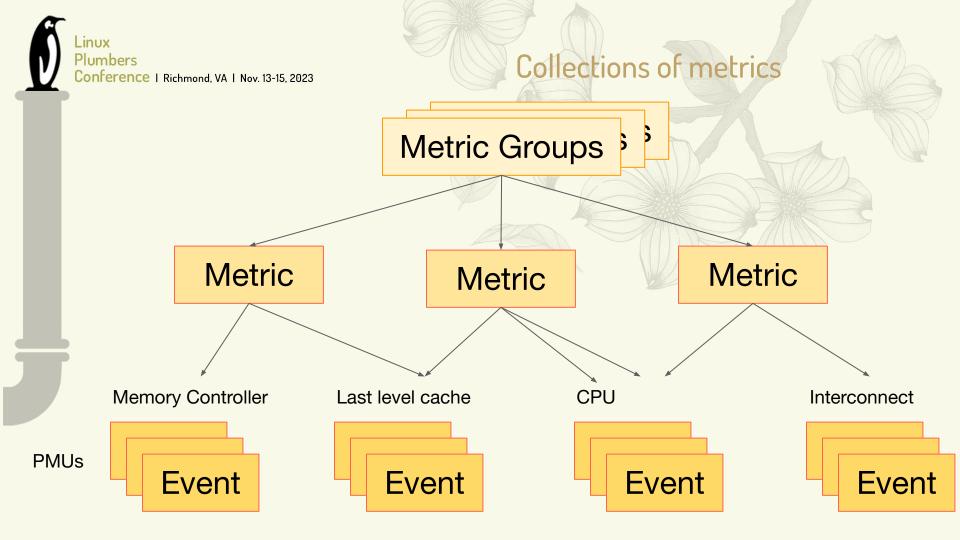

Metric Groups:

Backend: [Grouping from Top-down Microarchitecture Analysis Metrics spreadsheet] tma core bound [This metric represents fraction of slots where Core non-memory issues were of a bottleneck] [max(0, tma backend bound - tma memory bound)] [tma core bound > 0.1 & tma backend bound > 0.2] tma info core ilp [Instruction-Level-Parallelism (average number of uops executed when there is execution) per-core] [UOPS EXECUTED.THREAD / (UOPS EXECUTED.CORE CYCLES GE 1 / 2 if #SMT on else UOPS EXECUTED.CORE CYCLES GE 1)] tma info memory 12mpki [L2 cache true misses per kilo instruction for retired demand loads] [1e3 \* MEM LOAD RETIRED.L2 MISS / INST RETIRED.ANY]

```

$ perf list --details

...

Metric Groups:

```

#### Seeing metric expressions

Backend: [Grouping from Top-down Microarchitecture Analysi spreadsheet] Metric expression tma core bound [This metric represents fraction of slots where Core r memory issues were of a bottleneck] [max(0, tma backend bound - tma memory bound)] [tma core bound > 0.1 & tma backend bound > 0.2] tma info core ilp [Instruction-Level-Parallelism (average number of uops executed when there is execution) per-core] [UOPS EXECUTED.THREAD / (UOPS EXECUTED.CORE CYCLES GE 1 / 2 if #SMT on else UOPS EXECUTED.CORE CYCLES GE 1)] tma info memory 12mpki [L2 cache true misses per kilo instruction for retired demand loads] [1e3 \* MEM LOAD RETIRED.L2 MISS / INST RETIRED.ANY]

```

$ perf list --details

```

Seeing metric expressions

Metric Groups:

Backend: [Grouping from Top-down Microarchitecture Analysis spreadsheet] Threshold expression tma core bound [This metric represents fraction of slots where Core were of a bottleneck] [max(0, tma backend bound - tma memory bound)] [tma core bound > 0.1 & tma backend bound > 0.2] tma info core ilp [Instruction-Level-Parallelism (average number of uops executed when there is execution) per-core] [UOPS EXECUTED.THREAD / (UOPS EXECUTED.CORE CYCLES GE 1 / 2 if #SMT on else UOPS EXECUTED.CORE CYCLES GE 1)] tma info memory 12mpki [L2 cache true misses per kilo instruction for retired demand loads] [1e3 \* MEM LOAD RETIRED.L2 MISS / INST RETIRED.ANY]

TOPDOWN.SLOTS

#### The tma\_core\_bound metric

max(0, tma\_backend\_bound - tma\_memory\_bound)

(CYCLE\_ACTIVITY.STALLS\_MEM\_ANY + EXE\_ACTIVITY.BOUND\_ON\_STORES)

(CYCLE\_ACTIVITY.STALLS\_TOTAL + (EXE\_ACTIVITY.1\_PORTS\_UTIL +

tma\_retiring \* EXE\_ACTIVITY.2\_PORTS\_UTIL) +

EXE\_ACTIVITY.BOUND\_ON\_STORES) \* tma\_backend\_bound

topdown\-retiring / (topdown\-fe\-bound + topdown\-bad\-spec +

topdown\-retiring + topdown\-be\-bound) + 0 \* tma\_info\_thread\_slots

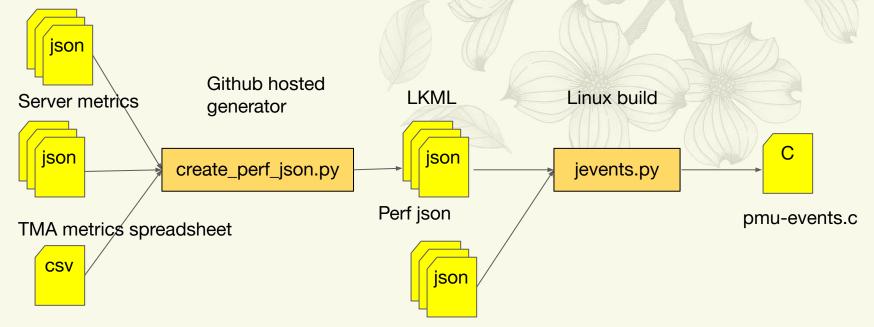

## Where do the events and metrics come from?

#### Per architecture event json

https://github.com/intel/perfmon

Perf json from other architectures

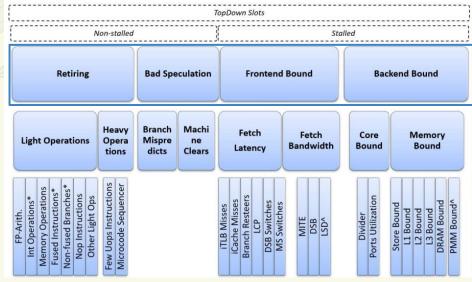

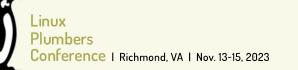

#### Top-down Microarchitecture Analysis (TMA)

#### TMA methodology

- Identifying performance bottlenecks in out-of-order cores

- No requiring deep knowledge of the microarchitecture details

- Available in Intel client and server platforms

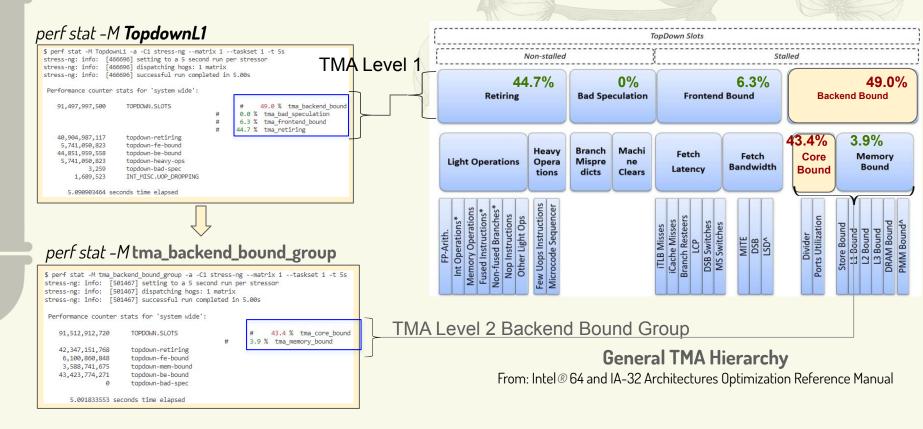

#### TMA in Linux Perf Tool

• Use `perf stat -M` to drill down

General TMA Hierarchy for Out-of-Order Microarchitecture

From: Intel® 64 and IA-32 Architectures Optimization Reference Manual

1. Intel® 64 and IA-32 Architectures Optimization Reference Manual, Appendix B.1

2. A. Yasin, A Top-Down method for performance analysis and counters architecture, ISPASS 2014

#### Example: TMA Level Breakdown with Linux Perf Tool

#### Example: TMA Level Breakdown with Linux Perf Tool

#### perf stat -M tma\_core\_bound\_group

#### Topdown is now present in perf stat default output

23.9 %

tma retiring

\$ perf stat true

#### (for Icelake and newer models)

Performance counter stats for 'true':

| 1.08     | msec | task-clock       |   | #    | 0.089   | CPUs utilized   |

|----------|------|------------------|---|------|---------|-----------------|

| 1        |      | context-switches |   | #    | 926.027 | /sec            |

| 0        |      | cpu-migrations   |   | #    | 0.000   | /sec            |

| 52       |      | page-faults      |   | #    | 48.153  | K/sec           |

| ,245,404 |      | cycles           |   | #    | 1.153   | GHz             |

| ,339,902 |      | instructions     |   | #    | 1.08    | insn per cycle  |

| 269,832  |      | branches         |   | #    | 249.872 | M/sec           |

| 7,143    |      | branch-misses    |   | #    | 2.65%   | of all branches |

|          |      | TopdownL1        | # | 24.6 | % tma_k | ackend_bound    |

|          |      |                  | # | 9.6  | % tma_k | ad_speculation  |

|          |      |                  | # | 41.9 | % tma_f | rontend_bound   |

#

0.012078534 seconds time elapsed

0.000000000 seconds user 0.003140000 seconds sys

#### Optionality of metric thresholds

Metric thresholds are themselves metrics. This means more events may be present when a threshold is computed which may cause event multiplexing.

To avoid multiplexing metric thresholds are computed:

- whenever all events are present,

- when a metric is explicitly requested except when -metric-no-threshold is passed.

#### Going from counts to samples

Counters, metrics and their thresholds indicate performance issues but samples show where in your code things are happening. Use "Sample with" from perf list to get the event to use with perf record.

#### \$ perf list -v

#### tma\_ports\_utilized\_1

[This metric represents fraction of cycles where the CPU executed total of 1 uop per cycle on all execution ports (Logical Processor cycles since ICL, Physical Core cycles otherwise). This can be due to heavy data-dependency among software instructions; or over oversubscribing a particular hardware resource. In some other cases with high 1\_Port\_Utilized and L1\_Bound; this metric can point to L1 data-cache latency bottleneck that may not necessarily manifest with complete execution starvation (due to the short L1 latency e.g. walking a linked list) - looking at the assembly can be helpful.Sample with: EXE\_ACTIVITY.1\_PORTS\_UTIL. Related metrics: tma\_l1\_bound]

#### Going from counts to samples

Counters, metrics and their thresholds indicate performance issues but samples show where in your code things are happening. Use "Sample with" from perf list to get the event to use with perf record.

#### \$ perf list -v

#### tma\_ports\_utilized\_1

[This metric represents fraction of cycles where the CPU executed total of 1 uop per cycle on all execution ports (Logical Processor cycles since ICL, Physical Core cycles otherwise). This can be due to heavy data-dependency among software instructions; or over oversubscribing a particular hardware resource. In some other cases with high 1\_Port\_Utilized and L1\_Bound; this metric can point to L1 data-cache latency bottleneck that may not necessarily manifest with complete execution starvation (due to the short L1 latency e.g. walking a linked list) - looking at the assembly can be helpful.Sample with: EXE ACTIVITY.1 PORTS UTIL. Related metrics: tma l1 bound]

\$ perf record -e EXE ACTIVITY.1 PORTS UTIL ...

#### #EBS\_Mode

Key part of TMA metrics is a measure of slots, number of functional units multiplied by cycles, pre-Icelake there was no counter for this. Hyperthreading complicated the slots calculation and counters were added measuring when 1 or both hyperthreads were active. EBS mode scaled metrics pre-Icelake accordingly, but was buggy unless in system-wide mode (ie. when no scaling was necessary). Because of the bugginess, the metrics are not enabled by default on pre-Icelake. TopdownL1 and other metrics are available pre-Icelake but some caution should be

observed when measuring benchmarks as EBS mode will be implicitly used.

\$ perf stat -a sleep 1

#### Support for hybrid processors

Performance counter stats for 'system wide':

```

24,081.38 msec cpu-clock

391

context-switches

25

cpu-migrations

68

page-faults

129,900,175

cpu atom/cycles/

cpu core/cycles/

16,045,550

cpu atom/instructions/

19,513,883

cpu core/instructions/

8,909,751

cpu atom/branches/

3,904,849

cpu core/branches/

1,870,930

662,455

cpu atom/branch-misses/

98,623

cpu core/branch-misses/

TopdownL1 (cpu core)

TopdownL1 (cpu atom)

```

# # #

#

# #

| # 23.984  | CPUs utilized        |          |

|-----------|----------------------|----------|

| # 16.237  | /sec                 |          |

| # 1.038   | /sec                 |          |

| # 2.824   | /sec                 |          |

| # 0.005   | GHz                  | (54.18%  |

| # 0.001   | GHz                  |          |

| # 0.15    | insn per cycle       | (63.34%  |

| # 0.07    | insn per cycle       |          |

| # 162.152 | K/sec                | (63.33%  |

| # 77.692  | K/sec                |          |

| # 16.96%  | of all branches      | (63.34%  |

| # 2.53%   | of all branches      |          |

| 30.3 % tm | na_backend_bound     |          |

| 8.4 % tm  | na_bad_speculation   |          |

| 49.6 % tm | na_frontend_bound    |          |

| 1.7 % tma | _retiring            |          |

| 20.8 % tm | na_bad_speculation   | (63.35%) |

| 37.7 % tm | na_frontend_bound    | (63.71%) |

| 35.4 % tm | na_backend_bound     |          |

| 35.4 % tm | na_backend_bound_aux | (64.11%) |

| 5.5 % tm  | na_retiring          | (64.15%) |

|           |                      |          |

\$ perf stat -a sleep 1

### Support for hybrid processors

Performance counter stats for 'system wide':

| 391       context-switches       #       16.237 /sec         25       cpu-migrations       #       1.038 /sec         68       page-faults       #       2.824 /sec         129,900,175       cpu_atom/cycles/       #       0.005 GHz       (54.18%)         16,045,550       cpu_atom/cycles/       #       0.001 GHz       (63.34%)         19,513,883       cpu_atom/instructions/       #       0.15 insn per cycle       (63.34%)         3,904,849       cpu_atom/branch       Per core type       .152 K/sec       (63.33%)         1,870,930       cpu_core/branch       breakdown       .692 K/sec       .692 K/sec         98,623       cpu_core/branch       breakdown       .53% of all branches       .63.34%)         98,623       cpu_core/branch       .53% of all branches       .63.34%)         11.7 %       tma_backend_bound       #       11.7 %       tma_frontend_bound         #       11.7 %       tma_frontend_bound       .63.35%)       #       .37.7 %       tma_frontend_bound       .63.71%)         #       35.4 %       tma_backend_bound       #       .5.5 %       tma_retiring       .64.11%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 24,081.38        | msec cpu-clock |                            | #    | 23.984       | CPUs utilized       |          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|----------------------------|------|--------------|---------------------|----------|

| 68       page-faults       #       2.824 /sec         129,900,175       cpu_atom/cycles/       #       0.005 GHz       (54.18%)         16,045,550       cpu_core/cycles/       #       0.001 GHz       (63.34%)         19,513,883       cpu_atom/instructions/       #       0.15 insn per cycle       (63.34%)         8,909,751       cpu_core/instru       0.07 insn per cycle       (63.33%)         1,870,930       cpu_core/branch       Per core type       .692 K/sec       .692 K/sec         662,455       cpu_atom/branch       breakdown       .96% of all branches       .63.34%)         98,623       cpu_core/branch       .53% of all branches       .63.34%)         TopdownL1       (cpu_atom)       #       8.4 % tma_bad_speculation       #         #       49.6 % tma_frontend_bound       #       11.7 % tma_retiring         TopdownL1       (cpu_atom)       #       20.8 % tma_bad_speculation       .63.35%)         #       37.7 % tma_frontend_bound       .63.71%)       #       35.4 % tma_backend_bound         #       35.4 % tma_backend_bound       .64.11%)       .64.11%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 391              | context-sw:    | itches                     | #    | 16.237       | /sec                |          |

| 129,900,175       cpu_atom/cycles/       #       0.005 GHz       (54.18%)         16,045,550       cpu_core/cycles/       #       0.001 GHz       (63.34%)         19,513,883       cpu_atom/instruction       #       0.001 GHz       (63.34%)         8,909,751       cpu_core/instruction       #       0.07 insn per cycle       (63.33%)         1,870,930       cpu_core/branch       Per core type       .152 K/sec       (63.33%)         662,455       cpu_atom/branch       breakdown       .692 K/sec       .96% of all branches       (63.34%)         98,623       cpu_core/branch       breakdown       .53% of all branches       (63.34%)         98,623       cpu_core/branch       #       8.4 % tma_bad_speculation       (63.34%)         TopdownL1       (cpu_atom)       #       20.8 % tma_frontend_bound       (63.35%)         #       37.7 % tma_frontend_bound       (63.71%)       #       35.4 % tma_backend_bound         #       35.4 % tma_backend_bound       #       (64.11%)       *                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25               | cpu-migrat:    | ions                       | #    | 1.038        | /sec                |          |

| <pre>16,045,550 cpu_core/cycles/</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 68               | page-fault:    | 5                          | #    | 2.824        | /sec                |          |

| 19,513,883 cpu_atom/instructions/<br>8,909,751 cpu_core/instru<br>3,904,849 cpu_atom/branch<br>1,870,930 cpu_core/branch<br>662,455 cpu_atom/branch<br>98,623 cpu_core/branch<br>TopdownL1 (cpu_core)<br># 8.4 % tma_bad_speculation<br># 49.6 % tma_frontend_bound<br># 11.7 % tma_retiring<br>TopdownL1 (cpu_atom)<br># 20.8 % tma_bad_speculation (63.35%)<br># 37.7 % tma_frontend_bound<br># 35.4 % tma_backend_bound<br># 35.4 % tma_backend_bound<br># 64.11%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 129,900,175      | cpu atom/cy    | ycles/                     | #    | 0.005        | GHz                 | (54.18%) |

| <pre>8,909,751 cpu_core/instru<br/>3,904,849 cpu_atom/branch<br/>1,870,930 cpu_core/branch<br/>662,455 cpu_atom/branch<br/>98,623 cpu_core/branch<br/>TopdownL1 (cpu_core)</pre> Per core type<br>breakdown <pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16,045,550       | cpu core/cy    | ycles/                     | #    | 0.001        | GHz                 |          |

| 3,904,849 cpu_atom/branch<br>1,870,930 cpu_core/branch<br>662,455 cpu_atom/branch<br>70pdownL1 (cpu_core)<br>4 8.4 % tma_bad_speculation<br>4 49.6 % tma_frontend_bound<br>4 11.7 % tma_retiring<br>70pdownL1 (cpu_atom)<br>4 20.8 % tma_bad_speculation<br>4 35.4 % tma_backend_bound<br>5 3% of all branches<br>5 4% tma_bad_speculation<br>6 40.11% | 19,513,883       | cpu_atom/in    | nstru <mark>ctions/</mark> | #    | <b>1</b> .15 | insn per cycle      | (63.34%) |

| 1,870,930 cpu_core/branch<br>662,455 cpu_atom/branch<br>98,623 cpu_core/branch<br>TopdownL1 (cpu_core)<br># 8.4 % tma_bad_speculation<br># 49.6 % tma_retiring<br>TopdownL1 (cpu_atom)<br># 20.8 % tma_bad_speculation (63.35%)<br># 37.7 % tma_frontend_bound<br># 35.4 % tma_backend_bound<br># 35.4 % tma_backend_bound_aux (64.11%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8,909,751        | cpu_core/i     | nstru                      |      | .07          | insn per cycle      |          |

| 1,010,550Cpu_core/branchbreakdown.052 k/sec662,455cpu_atom/branch.96% of all branches.63.34%)98,623cpu_core/branch.53% of all branches.53% of all branchesTopdownL1 (cpu_core)#8.4 % tma_bad_speculation#49.6 % tma_frontend_bound#11.7 % tma_retiringTopdownL1 (cpu_atom)#20.8 % tma_bad_speculation#37.7 % tma_frontend_bound#35.4 % tma_backend_bound#35.4 % tma_backend_bound#35.4 % tma_backend_bound_aux#35.4 % tma_backend_bound_aux#35.4 % tma_backend_bound_aux#35.4 % tma_backend_bound_aux#35.4 % tma_backend_bound_aux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3,904,849        | cpu_atom/b     | ranch Dev eeve             | 1    | .152         | K/sec               | (63.33%) |

| 98,623 cpu_core/branch<br>TopdownL1 (cpu_core)<br># 8.4 % tma_bad_speculation<br># 49.6 % tma_frontend_bound<br># 11.7 % tma_retiring<br>TopdownL1 (cpu_atom)<br># 20.8 % tma_bad_speculation (63.35%)<br># 37.7 % tma_frontend_bound (63.71%)<br># 35.4 % tma_backend_bound<br># 35.4 % tma_backend_bound                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1,870,930        | cpu_core/b     | Lanch                      |      | .692         | K/sec               |          |

| TopdownL1 (cpu_core)<br># 8.4 % tma_bad_speculation<br># 49.6 % tma_frontend_bound<br># 11.7 % tma_retiring<br>TopdownL1 (cpu_atom)<br># 20.8 % tma_bad_speculation (63.35%)<br># 37.7 % tma_frontend_bound (63.71%)<br># 35.4 % tma_backend_bound<br># 35.4 % tma_backend_bound                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 662 <b>,</b> 455 | cpu_atom/b     | ranch breakdo              | own  | .96%         | of all branches     | (63.34%) |

| <pre># 8.4 % tma_bad_speculation # 49.6 % tma_frontend_bound # 11.7 % tma_retiring TopdownL1 (cpu_atom) # 20.8 % tma_bad_speculation (63.35%) # 37.7 % tma_frontend_bound (63.71%) # 35.4 % tma_backend_bound # 35.4 % tma_backend_bound</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 98,623           | cpu_core/b     | ranch                      |      | .53%         | of all branches     |          |

| <pre># 49.6 % tma_frontend_bound # 11.7 % tma_retiring TopdownL1 (cpu_atom) # 20.8 % tma_bad_speculation (63.35%) # 37.7 % tma_frontend_bound (63.71%) # 35.4 % tma_backend_bound # 35.4 % tma_backend_bound</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Topdow           | nL1 (cpu_core) |                            |      | s tm         | a_backend_bound     |          |

| #       11.7 % tma_retiring         TopdownL1 (cpu_atom)       #       20.8 % tma_bad_speculation (63.35%)         #       37.7 % tma_frontend_bound (63.71%)         #       35.4 % tma_backend_bound         #       35.4 % tma_backend_bound         #       35.4 % tma_backend_bound                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                  |                | #                          | 8.4  | 1 % tm       | a_bad_speculation   |          |

| TopdownL1 (cpu_atom) # 20.8 % tma_bad_speculation (63.35%)<br># 37.7 % tma_frontend_bound (63.71%)<br># 35.4 % tma_backend_bound<br># 35.4 % tma_backend_bound_aux (64.11%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                  |                | #                          | 49.0 | 5 % tm       | a_frontend_bound    |          |

| # 37.7 % tma_frontend_bound (63.71%)<br># 35.4 % tma_backend_bound<br># 35.4 % tma_backend_bound_aux (64.11%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                | #                          | 11.7 | % tma        | _retiring           |          |

| <pre># 35.4 % tma_backend_bound<br/># 35.4 % tma_backend_bound_aux (64.11%)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Topdow           | nL1 (cpu_atom) | #                          | 20.8 | 8 % tm       | a_bad_speculation   | (63.35%) |

| # 35.4 % tma_backend_bound_aux (64.11%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                  |                | #                          | 37.  | 7 % tm       | a_frontend_bound    | (63.71%) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                | #                          | 35.4 | 1% tm        | a_backend_bound     |          |

| # 5.5 % tma_retiring (64.15%)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                  |                | #                          | 35.4 | 1 % tm       | a_backend_bound_aux | (64.11%) |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                  |                | #                          | 5.5  | 5 % tm       | a_retiring          | (64.15%) |

#### \$ perf stat -a sleep 1

### Support for hybrid processors

Performance counter stats for 'system wide':

| 24,081.38 msec<br>391<br>25<br>68<br>129,900,175<br>16,045,550 | context-swi<br>cpu-migrati<br>page-faults<br>cpu atom/cy | olexing on Atom<br>to insufficient<br>inters for both<br>own and branch | 1.038 /sec<br>2.824 /sec<br>0.005 GHz | (54.18%) |

|----------------------------------------------------------------|----------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------|----------|

| 19,513,883                                                     | cpu_atom/in                                              | events                                                                  | insn per cycle                        | (63.34%) |

| 8,909,751                                                      | cpu_core/in                                              |                                                                         | 0.07 insn per cycle                   |          |

| 3,904,849                                                      | cpu_atom/br <del>anches/</del>                           |                                                                         | # 162.152 K/sec                       | (63.33%) |

| 1,870,930                                                      | cpu_core/branches/                                       |                                                                         | # 77.692 K/sec                        |          |

| 662,455                                                        | cpu_atom/branch-mis                                      |                                                                         | <pre># 16.96% of all branches</pre>   | (63.34%) |

| 98,623                                                         | cpu_core/branch-mi                                       | sses/                                                                   | # 2.53% of all branches               |          |

| TopdownL1                                                      | (cpu_core)                                               | #                                                                       | 30.3 % tma_backend_bound              |          |

|                                                                |                                                          | #                                                                       | 8.4 % tma_bad_speculation             |          |

|                                                                |                                                          | #                                                                       | 49.6 % tma_frontend_bound             |          |

|                                                                |                                                          | # 11                                                                    | 1.7 % tma_retiring                    |          |

| TopdownL1                                                      | (cpu_atom)                                               |                                                                         | 20.8 % tma_bad_speculation            | (63.35%) |

|                                                                |                                                          |                                                                         | 37.7 % tma_frontend_bound             | (63.71%) |

|                                                                |                                                          |                                                                         | 35.4 % tma_backend_bound              |          |

|                                                                |                                                          | #                                                                       | 35.4 % tma_backend_bound_aux          | (64.11%) |

|                                                                |                                                          | #                                                                       | 5.5 % tma_retiring                    | (64.15%) |

# Validation tests

\$ perf test -v validation

```

107: perf metrics value validation:

--- start ---

. . .

Workload: perf bench futex hash -r 2 -s

Total metrics collected: 200

Non-negative metric count: 200

Total Test Count: 100

Passed Test Count: 100

Test validation finished. Final report:

"Workload": "perf bench futex hash -r 2 -s",

"Report":

"Metric Validation Statistics": {

"Total Rule Count": 100,

"Passed Rule Count": 100

},

"Tests in Category": {

"PositiveValueTest": {

"Total Tests": 200,

"Passed Tests": 200,

"Failed Tests": []

```

```

"RelationshipTest": {

"Total Tests": 5,

"Passed Tests": 5,

"Failed Tests": []

},

"SingleMetricTest": {

"Total Tests": 95,

"Passed Tests": 95,

"Failed Tests": []

},

"Errors": []

test child finished with 0

---- end ----

perf metrics value validation: Ok

```

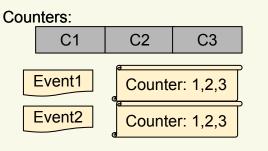

# Ongoing technical challenges

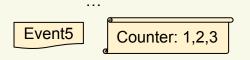

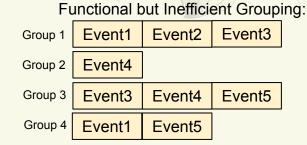

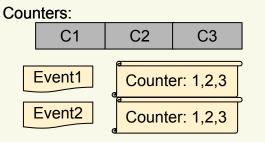

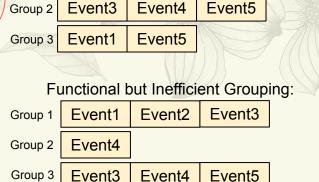

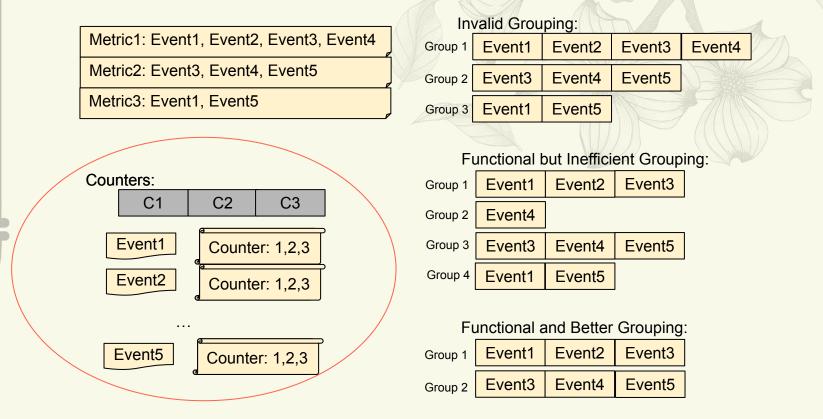

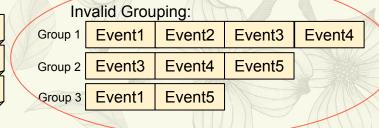

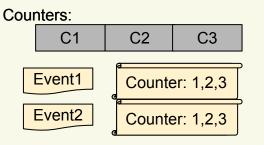

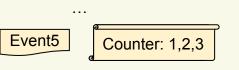

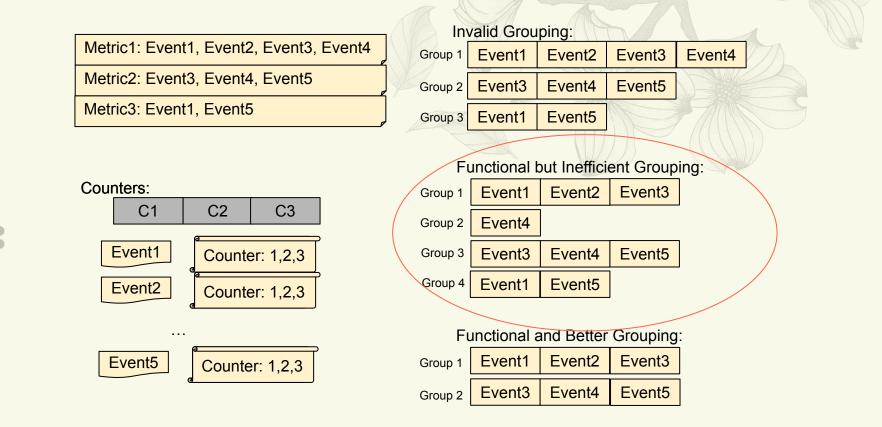

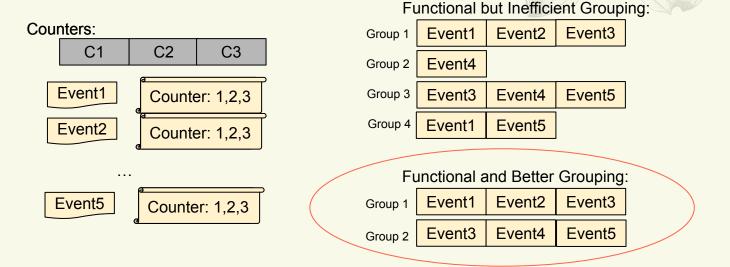

# Event grouping and hardware counters

Metric1: Event1, Event2, Event3, Event4

Metric2: Event3, Event4, Event5

Metric3: Event1, Event5

| In      | valid Grou | iping: |        | N      | 1 |

|---------|------------|--------|--------|--------|---|

| Group 1 | Event1     | Event2 | Event3 | Event4 | 2 |

| Group 2 | Event3     | Event4 | Event5 |        |   |

| Group 3 | Event1     | Event5 |        |        |   |

|         |            |        |        |        |   |

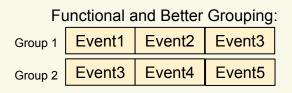

| Functional and Better Grouping: |        |        |        |  |  |  |

|---------------------------------|--------|--------|--------|--|--|--|

| Group 1                         | Event1 | Event2 | Event3 |  |  |  |

| Group 2                         | Event3 | Event4 | Event5 |  |  |  |

# Event grouping and hardware counters

Invalid Grouping:

Event1

Group 1

Metric1: Event1, Event2, Event3, Event4

Metric2: Event3, Event4, Event5

Metric3: Event1, Event5

Counter: 1,2,3

. . .

Event5

Event2

Event3

Event4

Group 4 Event1 Event5

| Functional and Better Grouping: |        |        |        |  |  |

|---------------------------------|--------|--------|--------|--|--|

| Group 1                         | Event1 | Event2 | Event3 |  |  |

| Group 2                         | Event3 | Event4 | Event5 |  |  |

## Event grouping and hardware counters

## Event grouping and hardware counters

Metric1: Event1, Event2, Event3, Event4

Metric2: Event3, Event4, Event5

Metric3: Event1, Event5

Functional but Inefficient Grouping:Group 1Event1Event2Event3Group 2Event4Event4Event5Group 3Event3Event4Event5Group 4Event1Event5

## Event grouping and hardware counters

## Event grouping and hardware counters

Metric1: Event1, Event2, Event3, Event4

Metric2: Event3, Event4, Event5

Metric3: Event1, Event5

| Invalid Grouping: |        |        |        |        |  |  |

|-------------------|--------|--------|--------|--------|--|--|

| Group 1           | Event1 | Event2 | Event3 | Event4 |  |  |

| Group 2           | Event3 | Event4 | Event5 | DEM    |  |  |

| Group 3           | Event1 | Event5 |        |        |  |  |

|                   |        |        |        |        |  |  |

# Hardware Aware Metric group Event Grouping

The key of **FUNCTIONAL** grouping is placing events to counters that support the events and avoid oversubscribed group

Information required to be hardware counter aware:

- Describe all counter restrictions from events in JSON files

- Static counter availability of one platform could be described in JSON files

- Dynamic counter availability needs to be resolved

2. Intel PMUs Event Reference: https://perfmon-events.intel.com/

<sup>1.</sup> Standardized metrics and events defined in JSON files - Project Valkyrie: <u>GitHub - intel/perfmon</u>

# Hardware Aware Metric group Event Grouping Details

#### Load Data From PMU-EVENTS

#### **Generate Groups**

- Build hardware counter information: PMU and counter availabilities

- Receive the event list of requested metrics

- Read counter restrictions of each event

- For each event, find a group for the correct PMU that has space

- Fill it into the group base on counter restrictions

- Create a new group if no space available in all the existing groups

#### Event Counter Restrictions for Reference:

1.Unit – The unit/core where the event is collected on.

2.Counter – The counters in the unit the event could be collected on and availability of the counters.

3.TakenAlone – TAKEN\_ALONE event cannot be collected in the same group with any other TAKEN\_ALONE events

4.Filter1 – Events collected in the same group need to have same filter1 value if applicable (SKX/CLX/CPX).

5.Fixed Counter – Do not group events use the same fixed counter in the same group.

6.0CR events – At most two 0CR events in one group.

**Output Result**

Generate metric

group grouping string

"Perf stat metric grouping with hardware information" RFC Patch: https://lore.kernel.org/all/20230925061824.3818631-1-weilin.wang@intel.com/

The key of **GOOD** grouping is high counter utilization and good locality of events for metrics

- High counter utilization => Less number of total groups => More time for each group Improve the overall event and metric accuracy

- Good locality of events => Events that required by one metric in the same or neighboring groups Improve metric accuracy

- However, these are conflicting conditions in some cases

#### Timed Processor Event Based Sampling (Timed PEBS)

- It records the number of unhalted core cycles between the retirement of the current instruction and the retirement of the prior instruction

- It significantly increases the accuracy of TMA

- IA32\_PERF\_CAPABILITIES.PEBS\_TIMING\_INF0[bit 17]

- Feature available in next generation Intel processors

#### Timed PEBS in perf tool

- Sampling mode upstreamed

- Retire\_lat is enabled as a weight of PMU events in perf record

- perf record -W -e event\_name:P

- Counting mode WIP

- Retire\_latency is included in some of the metrics in TMA for processors that support Timed PEBS

# What is Timed PEBS?

#### PEBS Basic Info Group

|          | Offset | Field Name          | Bits    |

|----------|--------|---------------------|---------|

|          | 0x0    | Record Format       | [31:0]  |

| <u>A</u> |        | Retire Latency      | [47:32] |

| 1        |        | Record Size         | [63:48] |

|          | 0x8    | Instruction Pointer | [63:0]  |

|          | 0x10   | Applicable Counters | [63:0]  |

|          | 0x18   | TSC                 | [63:0]  |

From:  $\operatorname{Intel}{\ensuremath{\mathcal{B}}}$  Architecture Instruction Set Extensions and Future Features

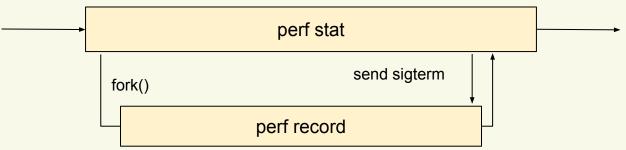

# **Counting mode Timed PEBS strategy**

# Enabling counting mode for Timed PEBS

- "Retire Latency" field in the PEBS record requires sampling

- Counting mode solution requires both perf record and perf stat

- Proposed method is to fork perf record within perf stat

- Perf stat process sampling data and capture the retire latency value, calculate and print out the final metric counts

Counting and Sampling in Parallel

- Sampled timings plus counters gives greatest accuracy for metrics but at the cost of using more counters.

- Current hard-coded values are for the worst case.

- Potential to use a variety of hard-coded values based on:

- Averages: mean, median

- Timings of similar benchmarks

- Periodic sampling of the system

- BPF vs perf record

# Questions

- Perf topdown

- Automate the drill down

- Perf record with the "Sample with"

- Support for non-CPU metrics

- ML in metrics, for example, I don't have instructions but I have branches. As there is usually a fixed ratio of branches to instructions can I swap a counter I don't have for one I do.

**Future Work**

# Linux Plumbers Conference

Richmond, Virginia | November 13-15, 2023

# Extra slides