# CXL 2.0 + Linux + QEMU = Yes

# CXL 2.0 + Linux + QEMU = Yes

# Introduction

### Last slide first!!!

AKE-CLARK.TUMBLR

# Agenda

- Introduction

- CXL 2.0 Background

Linux Driver Details

- QEMU

- Future

### Intro/Links

- Communications

- #cxl on OFTC

- <u>linux-cxl@vger.kernel.org</u>

- Drivers

- o <u>https://git.kernel.org/pub/scm/linux/kernel/git/cxl/cxl.git/</u>

- QEMU

- https://gitlab.com/bwidawsk/gemu

- https://github.com/pmem/run\_gemu

- Userspace

- <u>https://github.com/pmem/ndctl/tree/cxl-2.0v3</u>

- https://gitlab.com/bwidawsk-cxl/cxl\_rs

#### CXL 2.0 Background

#### Challenges

Industry trends driving demand for faster data processing and next-gen data center performance

Increasing demand for heterogeneous computing and server disaggregation

Need for increased memory capacity and bandwidth

Lack of open industry standard to address next-gen interconnect challenges

## **CXL** Features

CXL An open industry-supported cache-coherent interconnect for processors, memory expansion and accelerators

#### **Coherent Interface**

Leverages PCIe<sup>®</sup> with 3 mix-and-match protocols

#### Low Latency

.Cache and .Memory targeted at near CPU cache coherent latency

#### Asymmetric Complexity

Eases burdens of cache coherent interface designs

#### Challenges

Industry trends driving demand for faster data processing and next-gen data center performance

Increasing demand for heterogeneous computing and server disaggregation

Need for increased memory capacity and bandwidth

Lack of open industry standard to address next-gen interconnect challenges

### **CXL** Features

CXL An open industry-supported cache-coherent interconnect for processors, memory expansion and accelerators

#### **Coherent Interface**

Leverages PCIe<sup>®</sup> with 3 mix-and-match protocols

#### Low Latency

.Cache and .Memory targeted at near CPU cache coherent latency

#### Asymmetric Complexity

Eases burdens of cache coherent interface designs

Compute Express Link™ and CXL™ Consortium are trademarks of the Compute Express Link Consortium.

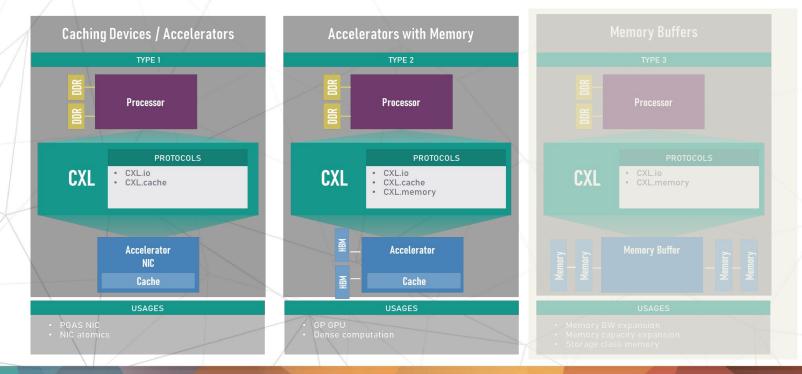

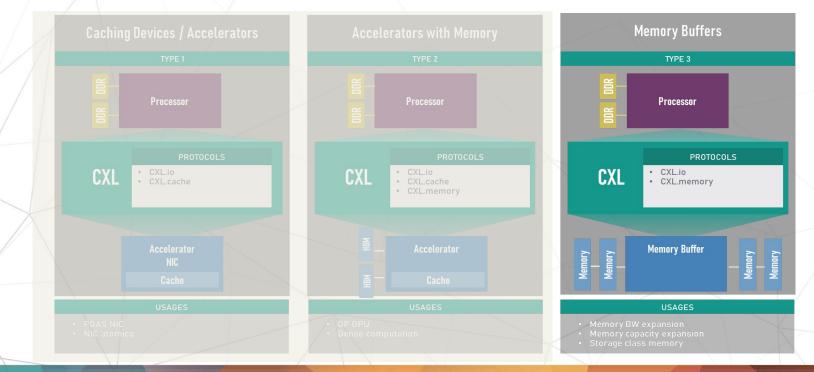

### Usage Models

### **Usage Models**

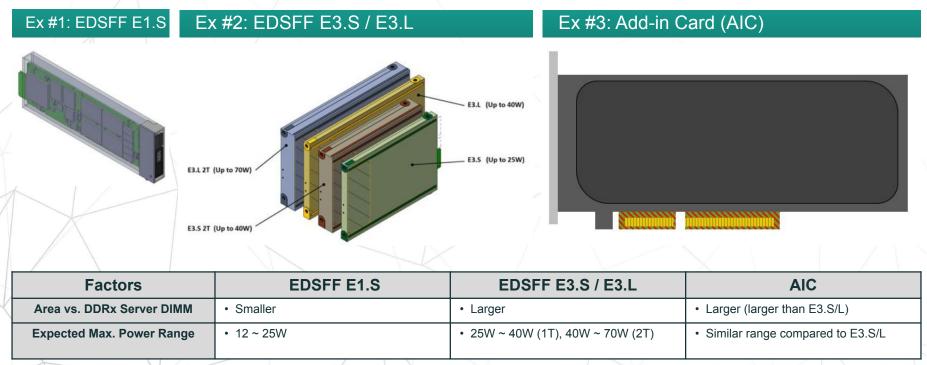

### **Form Factors**

Reference: snia.org

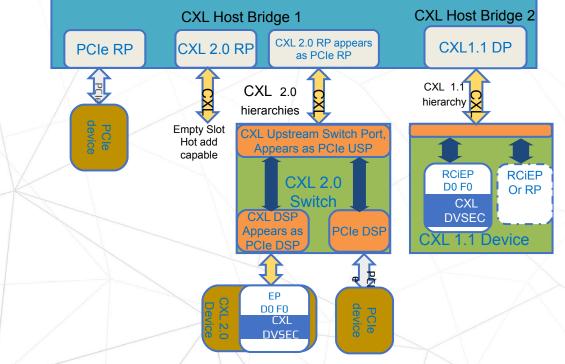

- **CXL Host Bridge 2 CXL Host Bridge 1** CXL 2.0 RP appears **CXL 2.0 RP** CXL1.1 DP PCIe RP as PCIe RP Ê CXL 1.1 CXL 2.0 hierarchy hierarchies PCle Empty Slot CXL Upstream Switch Port Hot add Appears as PCIe USP capable RCiEP RCiEP CXL 2.0 D0 F0 Or RP Switch CXL CXL DSP DVSEC PCIe DSP Appears as CXL 1.1 Device PCIe DSP ĴĔ EP D0 F0 PCle CXL DVSEC

- CXL 2.0 hierarchy appears like PCIe hierarchy

- Legacy PCI SW and CXL SW sees a RP or DSP with Endpoints below

- CXL link/interface errors are signaled to RP, not RCEC

- Port Control Override registers prevent legacy PCle software from unintentionally resetting the device and the link

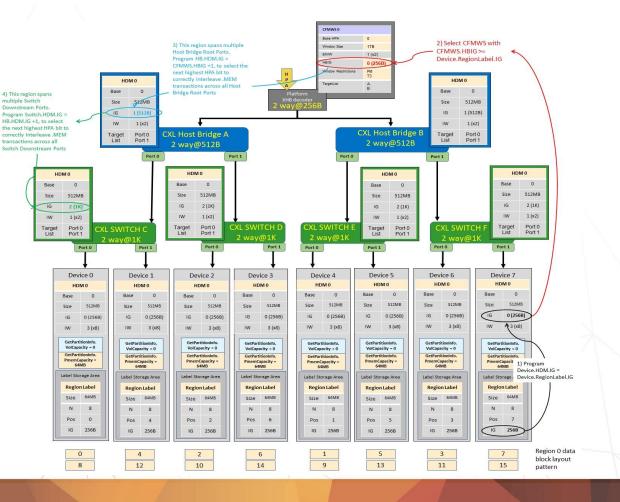

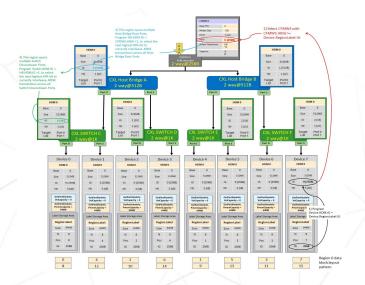

- Interleaving

- Cross host bridge

- Switch

- Device

### Interleave

# CXL Persistent Memory Devices

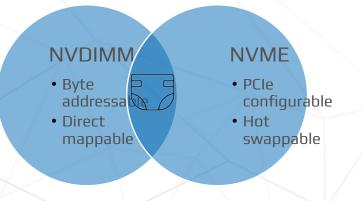

# PCI and NVDIMM had a coherent byte addressable baby... with atomics.

### PMEM

- **CXL** Generic **Mem Driver** OS I/F PCIe/CXI Bus Driver CXL 2.0 Mem I/F CXL Attached PMEN

- Persistent memory devices rely on System Software for provisioning and management

- CXL 2.0 introduces a standard register interface

- A generic memory device driver simplifies software enabling

- Architecture Elements

- Defined as number of discoverable Capabilities

- Capabilities includes Device Status and standard mailboxes, accessed via MMIO registers

- Standardized mailbox commands that cover errors/health, alerts, partitioning, passphrases etc.

- Allow Vendor specific extensions

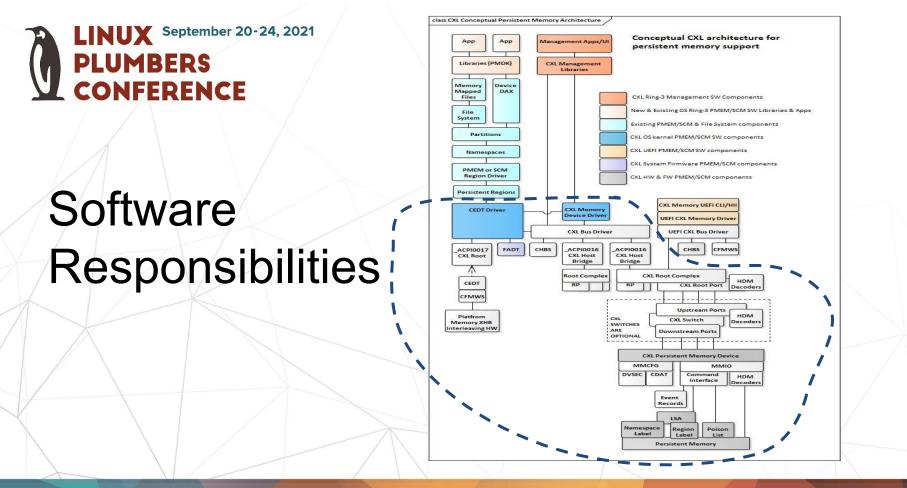

#### Linux Driver Details

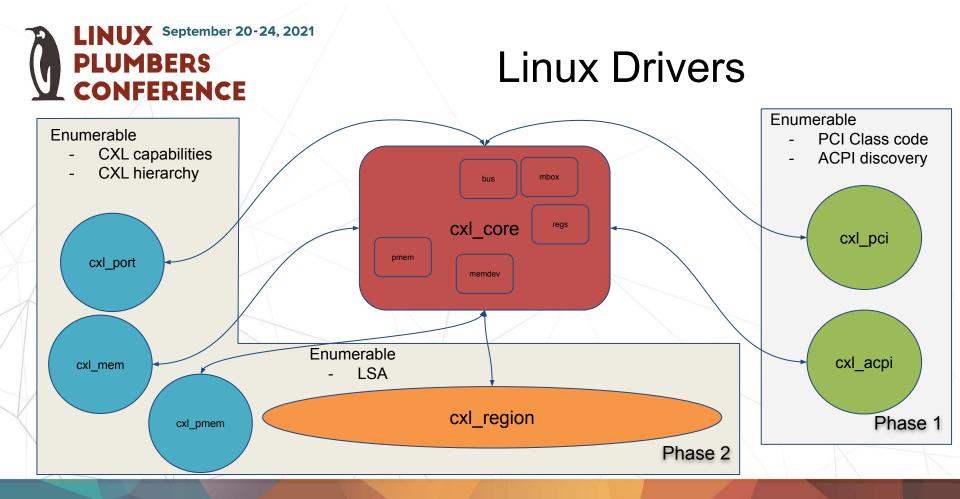

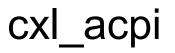

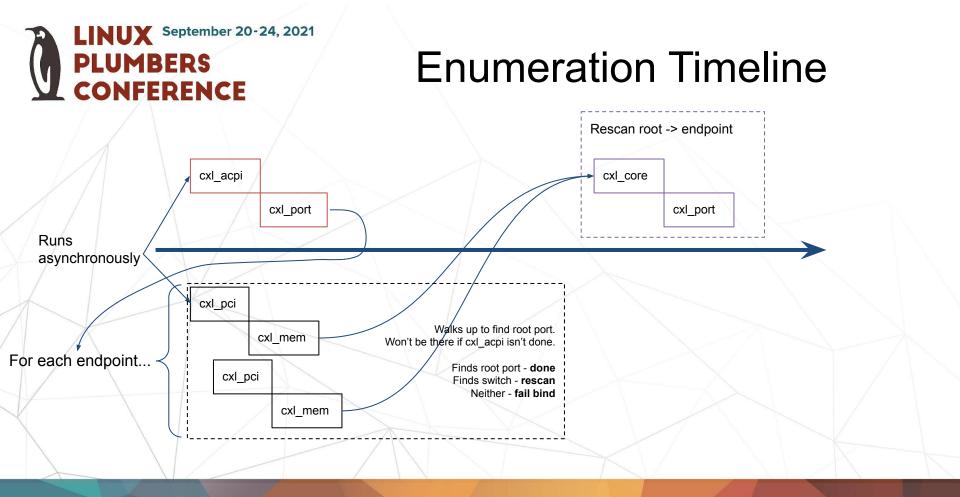

# SW Enumerable Components

- Maintains cxl\_driver infra

- Interfaces with LIBNVDIMM

- Manages device (sysfs)

- Services to add devices, ie. cxl\_decoder\_add()

- IOCTL interface

- Common functionality

- Mailbox controls (session layer)

- Register mapping

- Probed like a typical PCI device

- { PCI\_DEVICE\_CLASS((PCI\_CLASS\_MEMORY\_CXL << 8 | CXL\_MEMORY\_PROGIF), ~0)}</pre>

- CXL device manageability

- Implements mailbox transport (CXL) protocol

- Enumerates CXL device for subsequent driver

- cxl\_mem can't run until cxl\_pci is done

- Attestation/Security/Whatever

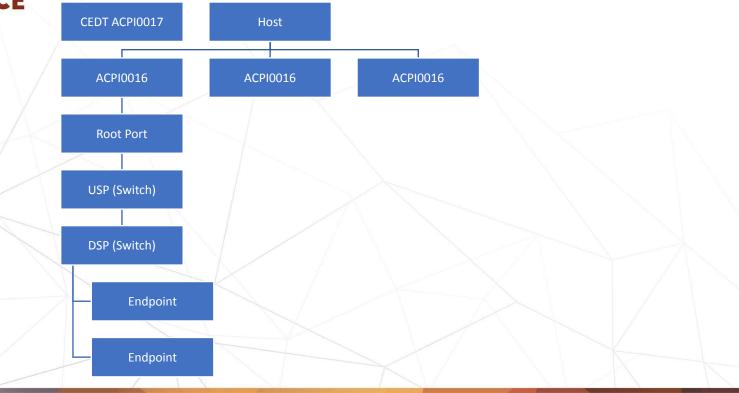

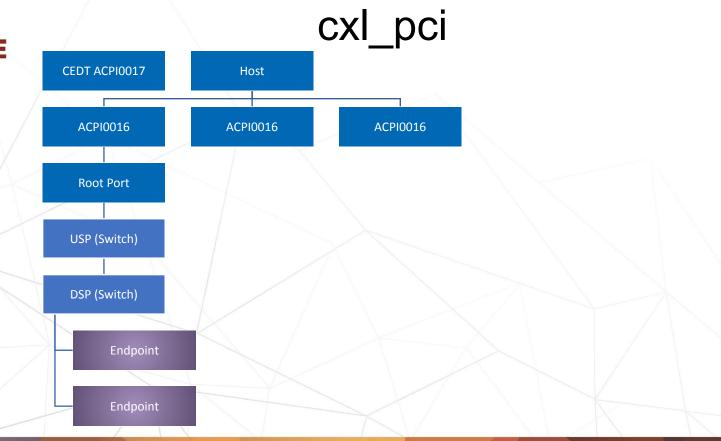

- Probed like a typical ACPI device

- { "ACPI0017", (unsigned long) &native\_acpi0017 },

- Platform specific CXL enumeration

- Mostly specified in UEFI, and CXL

- ACPI0017 starts enumeration of CXL ports

- CEDT

- "Root level" ports (platform)

- Hostbridges and root ports

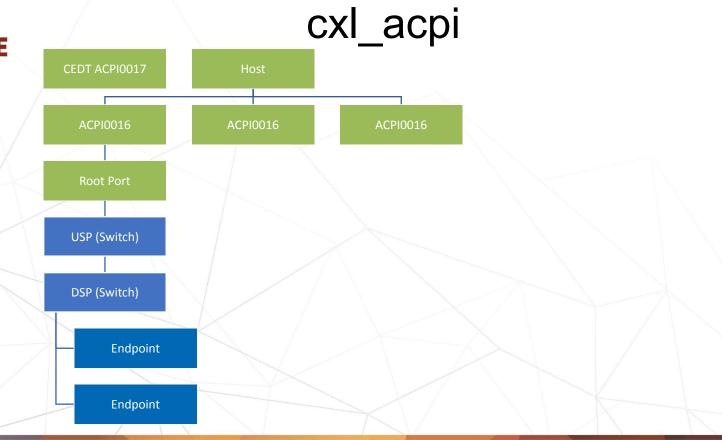

### cxl\_port

- Ports are created for all components with an "upstream port"

- Hostbridge

- Switch

- Endpoint

- Enumeration and control and control of decoder resources

- Provides as a service for other drivers

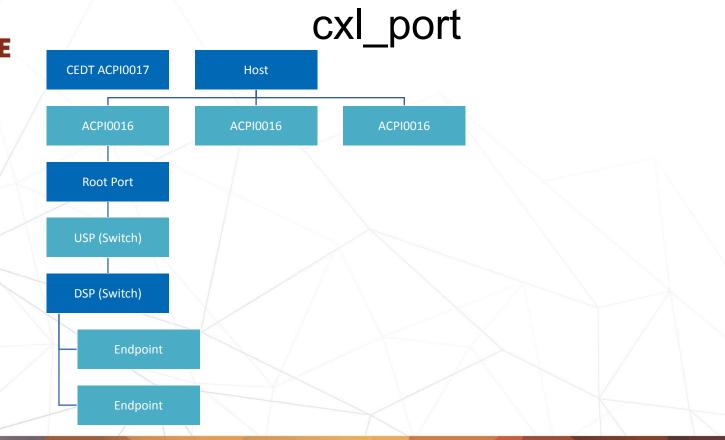

### cxl\_mem

- connects a device enumerated with cxl\_pci to CXL.mem.

Implements device functionality not handled by cxl\_pci

- "exports" if device is CXL.mem routed and enabled

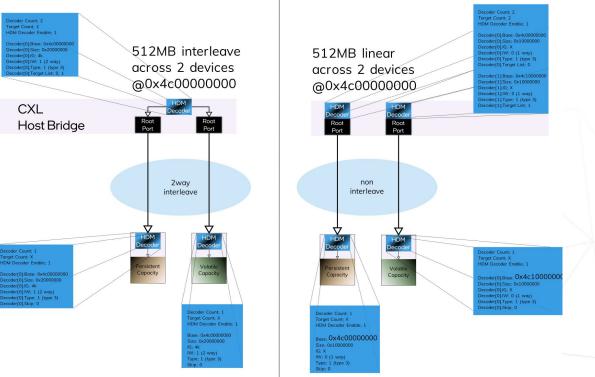

### Volatile vs. Persistent

|   |                                | Persistent   | Volatile     |                                                                                                                                                                             |

|---|--------------------------------|--------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 | Configured by BIOS             | ×            | $\checkmark$ | <ul> <li>BIOS configures all volatile capacities</li> <li>BIOS may check PMEM devices, but will not configure regions.</li> <li>BIOS may configure bootable PMEM</li> </ul> |

| 2 | OS managed                     | $\checkmark$ | •••          | <ul> <li>OS initializes persistent regions</li> <li>OS may create new persistent regions</li> <li>Manages hotplug, error, and reset sequences for both</li> </ul>           |

| 3 | Requires CXL.mem<br>capability |              | $\checkmark$ |                                                                                                                                                                             |

|   |                                |              | X            |                                                                                                                                                                             |

- Region

- Interleave set of devices 0

- Parameters (IG, HPA, etc) 0

- Stored in the Label Storage Area 0

- Creation

- Via sysfs ABI Ο

- Provisioned offline Ο

- Manufacture time

- Responsibilities

- Validating region configuration Programming HDM decoders Ο

- Ο

# Regions

# **Region Validation**

## **Decoder Programming**

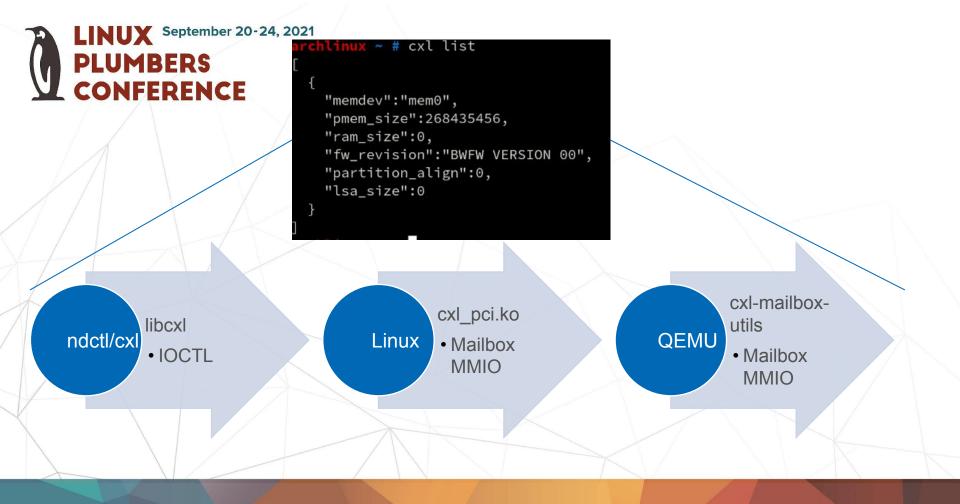

# **Linux Interfaces**

- Sysfs

- o /sys/bus/cxl/

- IOCTL

- QUERY

- SEND

- Managed command set

- RAW escape command

- Future

- Region Creation ABI

#### QEMU

### **Review Goals**

- 1) Upstream Linux Driver

- a) 0 days of spec release (v5.12)

i) Ease customer adoption

b) Backportable

- b) c) Platform aiding hw implementation and validation i) Validate the spec for driver usage

- Reusable past driver bringup 2)

- infra for regression testing Virtualization a)

- b)

- Scalable 3)

- **Community Contributions & Fixes** a)

### Pre-silicon State of the Art

- Hardware

- No 2.0 FPGAs available

- 1.1 is limited use and not readily available.

- Internal Simulation

- Delays/

- Can't work with community

- Prior art

- nfit\_test

- QEMU CCIX patches

### Pre-silicon State of the Art

- Hardware

- No 2.0 FPGAs available

- 1.1 is limited use and not readily available.

- Internal Simulation

- Delays/

- Can't work with community

- Prior art

- nfit\_test

- QEMU CCIX patches

This Photo by Unknown Author is licensed under <u>CC BY-SA</u>

#### LINUX September 20-24, 2021 PLUMBERS CONFERENCE

# **CXL** Arch Review

#### **LINUX** September 20-24, 2021 **PLUMBERS CONFERENCE**

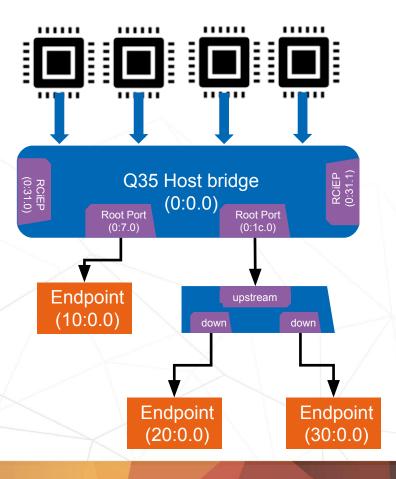

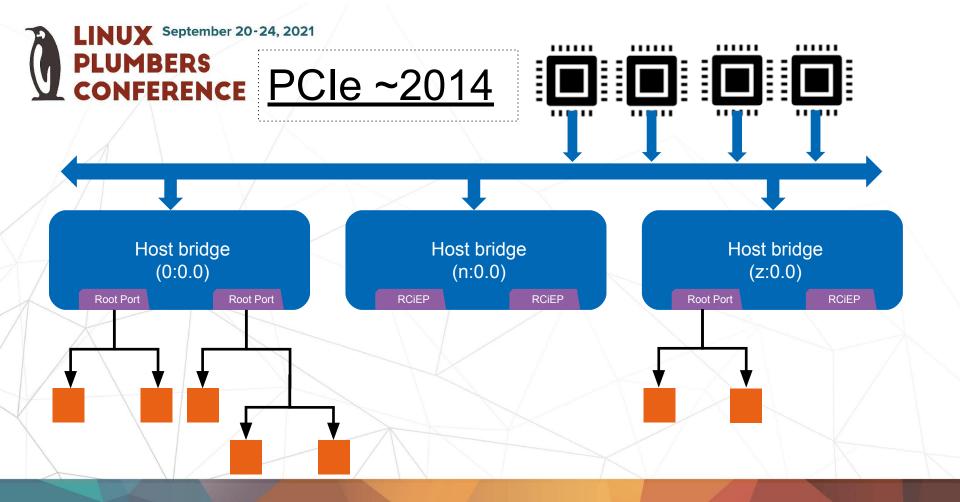

### PCIe in QEMU

#### What we all know and love

- Single root complex

- Endpoints

- Root ports

- Switches

- All traffic is funneled to the single host bridge

- QPI/UPI (not modeled)

## Options

#### Hacks to make Q35 - CXL 2.0

- Limited potential for interleave scenarios

- Touching Q35 is risky.

- Mistakes make everything work incorrectly.

- Replace Q35 with something newer

- Still Risky.

- A lot of work for not much gain

- What good does modeling UPI do for QEMU?

- Doubtful community wants it (support burden).

#### LINUX September 20-24, 2021 PLUMBERS CONFERENCE

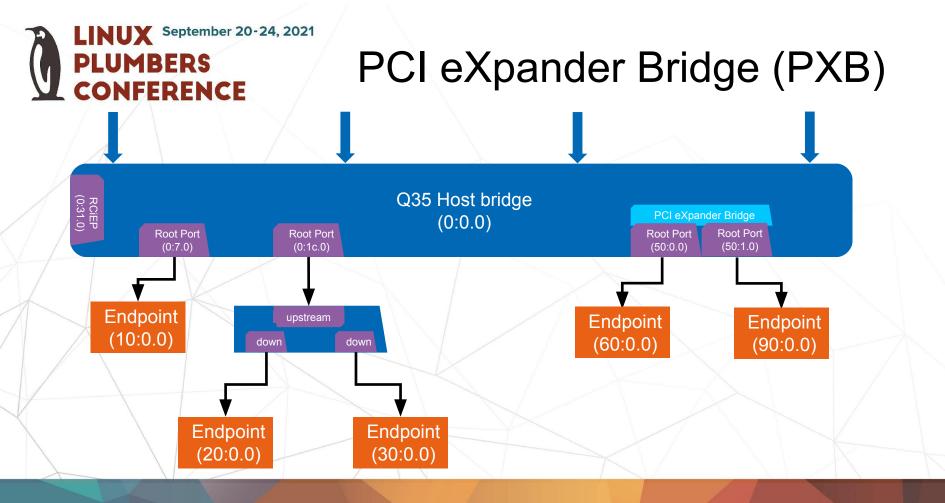

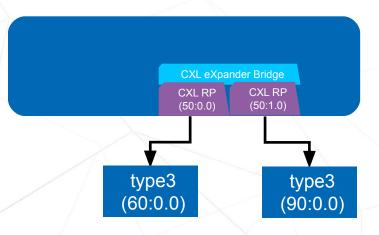

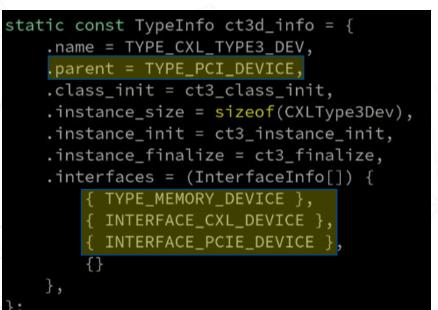

- CXL Type 3 device

- CXL Root Port

o hw/pci-bridge/cxl\_root\_port.c

CXL PXB

hw/pci-bridge/pci\_expander\_bridge.c

- NVDIMM & PCI had a baby...

- Inherits from both interfaces

- Mailbox handling

### November 10th 2020

### PATCHEOMBALLTHETHINGS

Spec Released QEMU patches submitted

- QEMU v3 patches sent

- v4 is ready for submission

- Community contributions for DOE, CDAT, and SPDM

- High bar for adding more

- Nothing exists quite like a CXL memory device

- Volatile + Persistent capacities

- Interleaving at multiple levels

- Linux phase 1 driver merged in 5.12

- Phase 2 actively being developed.

- Community contributions for DOE and CDAT

- Spec issues found and the fixes prototyped in QEMU

### Future

### What to do

- Community didn't adopt

- Minimal feedback

- Major reworks for interleave

- cxl\_test came along

- External contributions

- DOE

- CDAT

- SPDM

- Commercial Adoption...

### We're Hiring...

https://jobs.intel.com/ShowJob/Id/3089754/Linux-Kernel-Development-Engineer

#### • Linux

- DPA mapping (WIP)

Libnvdimm integration

- -- Librivainin integr

- Interleave

- Provisioning

- Recognition

- Hotplug

- Hot add

- Managed remove

- Asynchronous mailbox

- Userspace

- Testing

#### • QEMU

- Better tests

- Upstream/Downstream Ports

- Interleave Support

- Host bridge

- switch

- More firmware commands

- Hotplug support

- Error testing

- Interrupt support

- Memory class device overhaul

- Make Q35 CXL capable

- CXL type 1 and 2 devices

- CXL 1.1